#### US007851877B2

## (12) United States Patent

Tanaka et al.

# (10) **Patent No.:**

US 7,851,877 B2

(45) **Date of Patent:**

Dec. 14, 2010

# (54) LOGIC CIRCUIT AND SINGLE-ELECTRON SPIN TRANSISTOR

(75) Inventors: Masaaki Tanaka, Saitama (JP); Satoshi

Sugahara, Kanagawa (JP); Hai Nam

Pham, Tokyo (JP)

(73) Assignee: Japan Science and Technology Agency,

Kawaguchi-Shi (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 492 days.

(21) Appl. No.: 11/886,564

(22) PCT Filed: Feb. 2, 2006

(86) PCT No.: PCT/JP2006/301744

§ 371 (c)(1),

(2), (4) Date: **Dec. 28, 2007**

(87) PCT Pub. No.: WO2006/100835

PCT Pub. Date: Sep. 28, 2006

(65) **Prior Publication Data**

US 2009/0039401 A1 Feb. 12, 2009

#### (30) Foreign Application Priority Data

Mar. 24, 2005 (JP) ...... 2005-085260

(51) Int. Cl.

**H01L 29/82** (2006.01)

(52) **U.S. Cl.** ...... **257/421**; 257/30; 257/295;

257/E29.323

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,838,021    | A * | 11/1998 | Ancona 257/30         |

|--------------|-----|---------|-----------------------|

| 5,877,511    | A * | 3/1999  | Tanamoto et al 257/30 |

| 6,066,867    | A * | 5/2000  | Nakamura 257/295      |

| 6,787,795    | B2* | 9/2004  | Uchida et al 257/30   |

| 2004/0238808 | A1* | 12/2004 | Fraboulet et al       |

#### FOREIGN PATENT DOCUMENTS

| JP | A-11-168205   | 6/1999  |

|----|---------------|---------|

| JP | A-2004-281548 | 10/2004 |

#### OTHER PUBLICATIONS

Tomohiro Matsuno et al.; "Novel Reconfigurable Logic Gates Using Spin Metal-Oxide-Semiconductor Filed-Effect Transistors"; *Japanese Journal of Applied Physics*; vol. 43; No. 9A, 2004; pp. 6032-6037.

#### (Continued)

Primary Examiner—Victor A Mandala Assistant Examiner—Scott Stowe (74) Attorney, Agent, or Firm—Oliff & Berridge, PLC

#### (57) ABSTRACT

A logic circuit that can reconfigure its functions in a nonvolatile manner and a single-electron transistor to be used in the logic circuits are provided. The logic circuit has a single-electron spin transistor that includes: a source; a drain; an island that is provided between the source and the drain, and has tunnel junctions between the island and the source and drain; and a gate that is capacitively coupled to the island. In this logic circuit, at least one of the source, the drain, and the island includes a ferromagnetic material having a variable magnetization direction.

#### 44 Claims, 33 Drawing Sheets

## US 7,851,877 B2

Page 2

### OTHER PUBLICATIONS

Masaaki Tanaka, "Semiconductor spin-electronics—Current Status and future prospects-"; *Applied Physics*; vol. 73, No. 4 2004; pp. 514-515.

Marc Pirmann et al.; "Asymmetric tunable tunneling magnetoresistance in single-electron transistors"; *Journal of Magnetism and Magnetic Materials*; 219; 2000; pp. 104-108.

\* cited by examiner

Fig. 1

Fig. 2

Fig. 3

Fig. 4

Fig. 5

Fig. 6

Fig. 7

Fig. 10

Fig. 11

Fig. 12

**>** 194:INV2 ||| 160:SET1 168 7а Е 7aF / 170:SET2 500k Ω 500k Ω 500k Ω 500k Ω 165 169~ 175 Vdd \_ 188 164 162 🥕 174~ 2aF | 177 | 8aF | 177 1aF 8aF 166 152 / Vm -||1 190:INV1 130:SEST1 138 ] 500kΩ(5MΩ) -145 115 7aF l 7aF 140:SEST2 500k Q (5MQ) 500k \( \text{Q} \) 500k \( \text{2} \) 2aF 2-142 7 134 Vm7=bbV -||1 132~ 4aF 131 ||4aF 1aF 4aF 137a 147a -146b 136b 146a 150 151

Fig. 15

Fig. 16

Fig. 17

----- SEST1:P SEST2:AP

----- SEST1:AP SEST2:P

--- SEST1:P SEST2:P

Fig. 19

ļι 284 **7** 285 360:INV2 268 260:SET1 269 R 272 Vdd 288 264 262 ~ 274~ 27 267 / C<sub>1</sub>I 230:SEST3 254 352 .252 Vdd 258 234 236  $\mathbf{\omega}$ 350:INV1 200:SEST1 Vdd \_ 228 202 ~ 214 ~ 207a C. 207b 220 221

Fig. 2(

Fig. 21

Fig. 22

Fig. 23

Fig. 24

Fig. 26

Fig. 27

Fig. 28

Fig. 29

Fig. 33

Fig. 34A

Fig. 34B

1

#### LOGIC CIRCUIT AND SINGLE-ELECTRON SPIN TRANSISTOR

#### FIELD OF THE INVENTION

The present invention relates to logic circuits and singleelectron spin transistors, and more particularly, to a logic circuit that can reconfigure its functions and single-electron spin transistors

#### BACKGROUND OF THE INVENTION

Having short development cycles, logic circuits that can reconfigure functions according to programs have been used for mobile devices such as portable telephone devices. Also, 15 such logic circuits have been studied as the key devices of information systems with reprogrammable hardware. Reconfigurable logic circuits include circuits having FPGAs (Field Programmable Logic Arrays) of the LUT (Look Up Table) type or vMOS circuits. However, those circuits have the problems of being volatile and having a large number of elements.

To solve those problems, a circuit including spin transistors having spin-dependent conductivity, such as spin MOSFETs, is disclosed in Non-Patent Reference 1. The structure of a spin MOSFET is shown in FIG. 1(a) of Non-Patent Reference 1. A 25 spin MOSFET has the same structure as a MOSFET, except that the source and the drain contain a conductive ferromagnetic material. In a case where the magnetization directions of the source and the drain are parallel to each other (parallel arrangement), the output current is different from the output current observed in a case where the magnetization directions of the source and the drain are antiparallel to each other (antiparallel arrangement) (FIG. 1(b) of Non-Patent Reference 1).

A logic circuit that utilizes the variable conductance by 35 changing the magnetization directions to control the logic threshold value of an inverter circuit is disclosed (FIG. 8 of Non-Patent Reference 2: Conventional Technique 1). This inverter circuit has a spin MOSFET as one of the FETs. The magnetization arrangement of the spin MOSFET is switched 40 between the parallel arrangement and the antiparallel arrangement, so as to control the logic threshold value of the inverter circuit.

A logic circuit that has an AND circuit function and an OR circuit function by changing the magnetization arrangement 45 of the spin MOSFET with the use of the above inverter circuit is also disclosed (FIG. 2(a) of Non-Patent Reference 1: Conventional Technique 2). Further, a logic circuit that has all-symmetric Boolean functions (AND, OR, XOR, NAND, NOR, XNOR, ALLO, and ALL1) with the use of four spin 50 MOSFETs and three inverter circuits is disclosed (FIG. 4(a) of Non-Patent Reference 1: Conventional Technique 3).

In this specification, the low level of a logic circuit is represented by "0", the high level is represented by "1", and the intermediate level between the low level and the high level is represented by "0.5". "Analog inputs" are inputs of the intermediate level "0.5" as well as the inputs "0" and "1" to be input to a logic circuit (or an inverter circuit, for example), in response to a two-input "0" or "1" that is input to input terminals of the logic circuit. Also, "weighting of an analog input" is the rate at which the input of an input terminal is input to a transistor in a case where the logic circuit includes two or more transistors connected to the input terminals. By each conventional technique, a floating gate formed with a capacitance is used to make an analog input to the logic circuit of the conventional technique from a two-input input terminal. "Reconfiguring a logic circuit function in a nonvolatile

2

manner" is being able to change the logic threshold value in a nonvolatile manner in a case of an inverter circuit, for example, and is being able to switch between an AND circuit function and an OR circuit function in a nonvolatile manner in a case of a Boolean logic circuit, for example, where the same circuits are used.

#### [Non-Patent Reference 1]

Tomohiro Matsuno, Satoshi Sugahara, and Masaaki Tanaka, "Novel Reconfigurable Logic Gates Using Spin Metal-Oxide-Semiconductor Field-Effect Transistors", Japanese Journal of Applied Physics, Japan Society of Applied Physics, 2004, Vol. 43, No. 9A, p.p. 6032-6037

#### [Non-Patent Reference 2]

Masaaki Tanaka, "Semiconductor Spin Electronics", Applied Physics, Japan Society of Applied Physics, 2004, Vol. 73, No. 4, p.p. 514-515

A spin MOSFET, however, is based on a MOSFET and involves a large charge amount. Therefore, to make an analog input to a logic circuit including a spin MOSFET, it is necessary to use a large-area floating gate. For example, it is necessary to prepare a floating gate having an area 100 or more times as large as the area of one MOSFET. As a result, the area of the logic circuit becomes large. Moreover, since a spin MOSFET is based on a MOSFET, the current consumption and the area of each transistor are large.

#### DISCLOSURE OF THE INVENTION

It is therefore an object of the present invention to provide a logic circuit that can reconfigure the functions of a logic circuit in a nonvolatile manner and has a small circuit area and small power consumption, and to provide single-electron spin transistors to be used in the logic circuit.

The present invention provides a logic circuit that includes a single-electron spin transistor that has a source, a drain, an island that is provided between the source and the drain, and a gate that is capacitively coupled to the island, a tunnel junction being provided between the source and the island, another tunnel junction being provided between the drain and the island. In this logic circuit, at least one of the source, the drain, and the island includes a ferromagnetic material having a reversible magnetization direction. In accordance with the present invention, the conductance between the source and the drain can be controlled by changing the magnetization direction of the single-electron spin transistor. By doing so, a logic circuit that can reconfigure functions in a nonvolatile manner can be provided. Further, as the single-electron spin transistor is employed, a logic circuit that has a small circuit area and small power consumption can be provided.

In this logic circuit, the source and the drain of the single-electron spin transistor may include ferromagnetic materials magnetized in the same direction, and the island may include the ferromagnetic material having the variable magnetization direction. With this arrangement, the conductance between the source and the drain can be certainly controlled, and a logic circuit that is suitable for reconfiguring the functions of a logic circuit in a nonvolatile manner can be provided.

In this logic circuit, the single-electron spin transistor may further include a substrate, the island, the source, the drain, and the gate may be formed on the substrate, the source, the drain, and the gate may be formed on sides of the island, and the gate may be capacitively coupled to the island via a space existing between the gate and the island. With this arrangement, the area of the gate capacitance can be made smaller, and the circuit area can be made smaller.

In this logic circuit, the single-electron spin transistor may further include a substrate, the source, the drain, and the island may be stacked on the substrate, the gate may be formed on a side of the island, and the gate may be capacitively coupled to the island via a space existing between the gate and the island. With this arrangement, the area of the gate capacitance can be made smaller, and the circuit area can be made smaller.

In this logic circuit, a logic circuit function may be reconfigured in a nonvolatile manner by changing the variable 10 magnetization direction of the ferromagnetic material of the single-electron spin transistor. In accordance with the present invention, a logic circuit that can reduce the circuit area and the power consumption can be provided by employing the single-electron spin transistor.

In this logic circuit, the logic circuit function is a logic threshold value of an inverter circuit or a function of a Boolean logic circuit.

This logic circuit may include: a plurality of input terminals; and a plurality of single-electron spin transistors, each of the single-electron spin transistors being the above described single-electron spin transistor. In this logic circuit, the weighting of analog inputs from the plurality of input terminals to the plurality of single-electron spin transistors may be performed with a plurality of gate capacitances of the respective single-electron spin transistors connected to the respective input terminals. In accordance with the present invention, analog inputs can be formed with the gate capacitances between the gates and the islands. Thus, a logic circuit that does not require a floating gate and has a small circuit area can be provided.

This logic circuit may further include a first inverter circuit that includes: a first single-electron spin transistor that has a source connected to an output terminal, a gate connected to an input terminal, and a drain connected to a first power supply 35 terminal; and a second single-electron spin transistor that has a drain connected to the output terminal, a gate connected to the input terminal, and a source connected to a second power supply terminal. In this first inverter circuit, each of the first single-electron spin transistor and the second single-electron spin transistor is the above described single-electron spin transistor.

In this logic circuit, when "0" is input to the input terminal, the first single-electron spin transistor is switched on, and the second single-electron spin transistor is switched off. When 45 "1" is input to the input terminal, the first single-electron spin transistor is switched off, and the second single-electron spin transistor is switched on.

In this logic circuit, the first inverter circuit controls the logic threshold value in a case where a magnetization 50 arrangement of the first single-electron spin transistor is a parallel arrangement while a magnetization arrangement of the second single-electron spin transistor is an antiparallel arrangement, and in a case where the magnetization arrangement of the first single-electron spin transistor is an antiparallel arrangement while the magnetization arrangement of the second single-electron spin transistor is a parallel arrangement.

In the first inverter circuit of this logic circuit, the input terminal may include a first input terminal and a second input 60 terminal, and the combination of an input to the first input terminal and an input to the second input terminal may be analog inputs to the first inverter circuit.

In the first inverter circuit of this logic circuit, the first input terminal may be connected to a first gate of the first singleelectron spin transistor and to a first gate of the second singleelectron spin transistor, and the second input terminal may be 4

connected to a second gate of the first single-electron spin transistor and to a second gate of the second single-electron spin transistor.

In the first inverter circuit of this logic circuit, the weighting of an analog input of an input from the first input terminal to the first single-electron spin transistor may be substantially the same as the weighting of an analog input of the input from the first input terminal to the second single-electron spin transistor, and the weighting of an analog input of an input from the second input terminal to the first single-electron spin transistor may be substantially the same as the weighting of an analog input of the input from the second input terminal to the second single-electron spin transistor.

In the first inverter circuit of this logic circuit, the capacitance value of a first gate capacitance of the first single-electron spin transistor may be substantially the same as the capacitance value of a first gate capacitance of the second single-electron spin transistor, and the capacitance value of a second gate capacitance of the first single-electron spin transistor may be substantially the same as the capacitance value of a second gate capacitance of the second single-electron spin transistor.

In the first inverter circuit of this logic circuit, the weighting of the analog inputs of the input from the first input terminal to the first single-electron spin transistor and the second single-electron spin transistor may be substantially the same as the weighting of the analog inputs of the input from the second input terminal to the first single-electron spin transistor and the second single-electron spin transistor. With this arrangement, a logic circuit that can reconfigure all-symmetric Boolean functions in a nonvolatile manner can be provided.

In the first inverter circuit of this logic circuit, the capacitance values of the first gate capacitance of the first single-electron spin transistor may be substantially same as the first gate capacitance of the second single-electron spin transistor, and the capacitance values of the second gate capacitance of the first single-electron spin transistor may be substantially same as the second gate capacitance of the second single-electron spin transistor. With this arrangement, a logic circuit that can reconfigure a symmetric Boolean function in a non-volatile manner can be provided.

In the first inverter circuit of this logic circuit, the weighting of the analog inputs of the input from the first input terminal to the first single-electron spin transistor and the second single-electron spin transistor may be different from the weighting of the analog inputs from the second input terminal to the first single-electron spin transistor and the second single-electron spin transistor. With this arrangement, a logic circuit that can reconfigure a asymmetric Boolean function in a nonvolatile manner can be provided.

In the first inverter circuit of this logic circuit, the capacitance values of the first gate capacitance of the first single-electron spin transistor and the first gate capacitance of the second single-electron spin transistor may be different from the capacitance values of the second gate capacitance of the first single-electron spin transistor and the second gate capacitance of the second single-electron spin transistor. With this arrangement, a logic circuit that can reconfigure a asymmetric Boolean function in a nonvolatile manner can be provided

In this logic circuit, the first inverter circuit may have the function of a two-input NOR circuit in a case where the magnetization arrangement of the first single-electron spin transistor is the antiparallel arrangement while the magnetization arrangement of the second single-electron spin transistor is the parallel arrangement, and the first inverter circuit

may have the function of a two-input NAND circuit in a case where the magnetization arrangement of the first single-electron spin transistor is the parallel arrangement while the magnetization arrangement of the second single-electron spin transistor is the antiparallel arrangement. With this arrangement, a logic circuit that can reconfigure a two-input NOR circuit function and a two-input NAND circuit function in a nonvolatile manner can be provided.

In this logic circuit, the output terminal of the first inverter circuit may be connected to an input terminal of a second inverter circuit, to form a two-input OR circuit function and a two-input AND circuit function. With this arrangement, a logic circuit that can reconfigure a two-input OR circuit function and a two-input AND circuit function in a nonvolatile manner can be provided.

In this logic circuit, the second inverter circuit may be an inverter circuit including a single-electron transistor. With this arrangement, the logic circuit can function as a logic circuit with higher accuracy, even if the output from the first inverter circuit is small.

This logic circuit may further include: a third single-electron spin transistor that has a source connected to the output terminal of the first inverter circuit and a drain connected to a third power supply terminal; and a fourth single-electron spin transistor that has a drain connected to the output terminal of 25 the first inverter circuit and a source connected to a fourth power supply terminal. In this logic circuit, each of the third single-electron spin transistor and the fourth single-electron spin transistor is the above described single-electron spin transistor.

In this logic circuit, when "0" is output from the first inverter circuit, the third single-electron spin transistor is switched on, and the fourth single-electron spin transistor is switched off. When "1" is output from the first inverter circuit, the third single-electron spin transistor is switched off, and 35 the fourth single-electron spin transistor is switched on.

This logic circuit may further include: a third inverter circuit that has an input terminal connected to the first input terminal and the second input terminal of the first inverter circuit, an output terminal connected to a gate of the third single-electron spin transistor, and has a logic threshold value greater than 0.5; and a fourth inverter circuit that has an input terminal connected to the first input terminal and the second input terminal of the first inverter circuit, an output terminal connected to a gate of the fourth single-electron spin transistor, and has a logic threshold value smaller than 0.5.

In this logic circuit, the weighting of analog inputs from the first input terminal and the second input terminal to the third inverter circuit, and the weighting of analog inputs from the first input terminal and the second input terminal to the fourth 50 inverter circuit may be substantially the same as the weighting of analog inputs from the first input terminal and the second input terminal to the first inverter circuit. With this arrangement, a logic circuit that can reconfigure all symmetric Boolean functions in a nonvolatile manner can be provided.

In this logic circuit, each of the third inverter circuit and the fourth inverter circuit may be an inverter circuit including a single-electron transistor. With this arrangement, the circuit area and the power consumption can be made smaller.

This logic circuit may further include a fifth inverter circuit that has an input terminal connected to the output terminal of the first inverter circuit. With this arrangement, a logic circuit that can reconfigure all symmetric Boolean functions in a nonvolatile manner with higher accuracy can be provided.

In this logic circuit, the fifth inverter circuit may be an inverter circuit including a single-electron transistor. With

6

this arrangement, the logic circuit can function as a logic circuit with higher certainty, even if the output from the first inverter circuit is small.

This logic circuit may have a circuit that can realize all symmetric Boolean functions by switching the magnetization arrangement of each of the first single-electron spin transistor, the second single-electron spin transistor, the third single-electron spin transistor, and the fourth single-electron spin transistor, between the parallel arrangement and the antiparallel arrangement.

The present invention also provides a single-electron spin transistor that includes: a substrate; a source that is formed on the substrate; an island that is formed on the source and has a tunnel junction between the source and the island; a drain that is formed on the island and has a tunnel junction between the island and the drain; and a gate that is formed on a side of the island, and is capacitively coupled to the island via a space existing between the island and the gate. In this single-electron spin transistor, at least one of the source, the drain, and the island includes a ferromagnetic material having a variable magnetization direction. In accordance with the present invention, the film thickness of each layer can be controlled with precision. Accordingly, the degree of freedom in transistor design is increased, and desired characteristics can be readily obtained. Also, as a transistor is formed in the vertical direction, the transistor area is made smaller, and the higher integration can be achieved.

The present invention also provides a single-electron spin transistor that includes: a substrate; a drain that is formed on the substrate; an island that is formed on the drain and has a tunnel junction between the drain and the island; a source that is formed on the island and has a tunnel junction between the island and the source; and a gate that is formed on a side of the island, and is capacitively coupled to the island via a space existing between the island and the gate. In this single-electron spin transistor, at least one of the source, the drain, and the island includes a ferromagnetic material having a variable magnetization direction. In accordance with the present invention, the film thickness of each layer can be controlled with precision. Accordingly, the degree of freedom in transistor design is increased, and desired characteristics can be readily obtained. Also, as a transistor is formed in the vertical direction, the transistor area is made smaller, and the higher integration can be achieved.

In this single-electron spin transistor, the source and the drain include ferromagnetic materials magnetized in the same direction, and the island includes the ferromagnetic material having the variable magnetization direction. In accordance with the present invention, a variation in threshold current caused by applying the spin injection magnetization reversal method can be restrained.

In this single-electron spin transistor, the magnetization direction of the island may be changed by injecting carriers from the source or the drain into the island. In accordance with the present invention, the power consumption for changing the magnetization direction of the island can be reduced.

In this single-electron spin transistor, one of the source and the drain may have a greater film thickness than the other one of the source and the drain. In accordance with the present invention, the magnetization direction of the island can be changed from the antiparallel arrangement to the parallel arrangement by injecting carriers from one of the source and the drain that has the greater film thickness, to the other one of the source and the drain. The magnetization direction of the island can be changed from the parallel arrangement to the antiparallel arrangement by injecting carriers from one of the

source and the drain that has the smaller film thickness, to the other one of the source and the drain.

In this single-electron spin transistor, one of the source and the drain may have a higher spin polarization rate than the other one of the source and the drain. In accordance with the present invention, the magnetization direction of the island can be changed from the antiparallel arrangement to the parallel arrangement by injecting carriers from one of the source and the drain that has the higher spin polarization rate, to the other one of the source and the drain. The magnetization direction of the island can be changed from the parallel arrangement to the antiparallel arrangement by injecting carriers from one of the source and the drain that has the lower spin polarization rate, to the other one of the source and the drain.

In this single-electron spin transistor, the island may be a single-electron spin transistor that is a carrier-induced ferromagnetic semiconductor film. In accordance with the present invention, the carrier density in the island is changed by adjusting the electric field applied on the island, so that the magnetization of the island can be more easily changed.

In this single-electron spin transistor, the gate is provided on either side of the island; and the magnetization direction of the island is changed by applying a voltage between the gates and injecting carriers from the source or the drain into the island. In accordance with the present invention, the power consumption for changing the magnetization direction of the island can be further reduced.

In this single-electron spin transistor, the voltage applied 30 between the gates is such a voltage as to reduce carrier density in the island. In accordance with the present invention, the carrier density in the island is reduced, and the magnetization of the island becomes smaller. Accordingly, the power consumption for changing the magnetization direction of the 35 island can be further reduced.

As described above, in accordance with the present invention, the conductance of a single-electron spin transistor can be controlled by changing the magnetization direction of the single-electron spin transistor. With this arrangement, a logic circuit that can reconfigure a logic circuit function in a nonvolatile manner can be provided. Further, as the charge amount to be controlled in a single-electron spin transistor, analog inputs can be made by combining the small gate capacitances between the gates and the island. Accordingly, 45 there is no need to employ a floating gate having a large area. With this arrangement, a very small circuit area can be realized. Also, as a single-electron spin transistor deals with single electrons, the power consumption is small, and the area of the transistor can be made small. Thus, a logic circuit and  $\,^{50}$ a single-electron spin transistor that can reconfigure logic circuit functions in a nonvolatile manner and have small circuit areas and small power consumption can be provided.

### BRIEF DESCRIPTION OF THE DRAWINGS

- FIG. 1 is a schematic view of the structure of a singleelectron spin transistor (SEST) used in embodiments of the present invention;

- FIG. 2 shows the circuit symbols of a single-electron spin transistor (SEST) used in embodiments of the present invention:

- FIG. 3 is a circuit diagram showing the resistance values and the capacitance values of a single-electron spin transistor 65 (SEST), with a simulation of the current-voltage characteristics being performed;

8

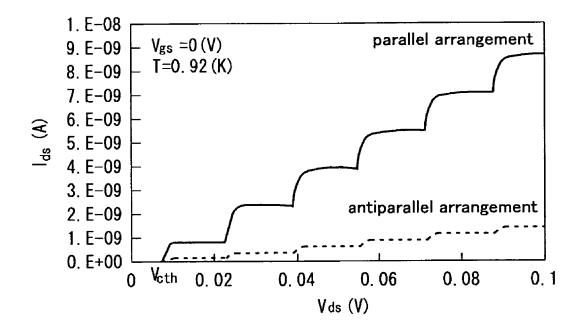

- FIG. 4 shows the results of a simulation of the characteristics of the drain current and the drain voltage of a single-electron spin transistor (SEST);

- FIG. 5 shows the results of a simulation of the characteristics of the drain current and the gate voltage of a single-electron spin transistor (SEST);

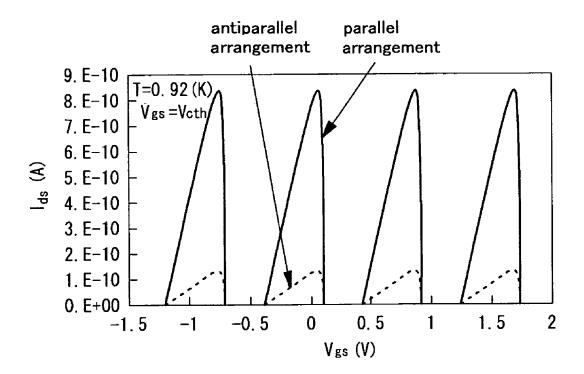

- FIG. **6** is a schematic cross-sectional view illustrating the method for manufacturing a single-electron spin transistor (SEST) to be used in embodiments;

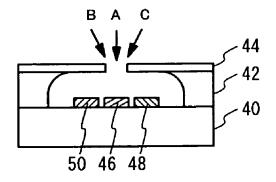

- FIG. 7 is a top view showing the structure of a single-electron spin transistor (SEST) to be used in embodiments;

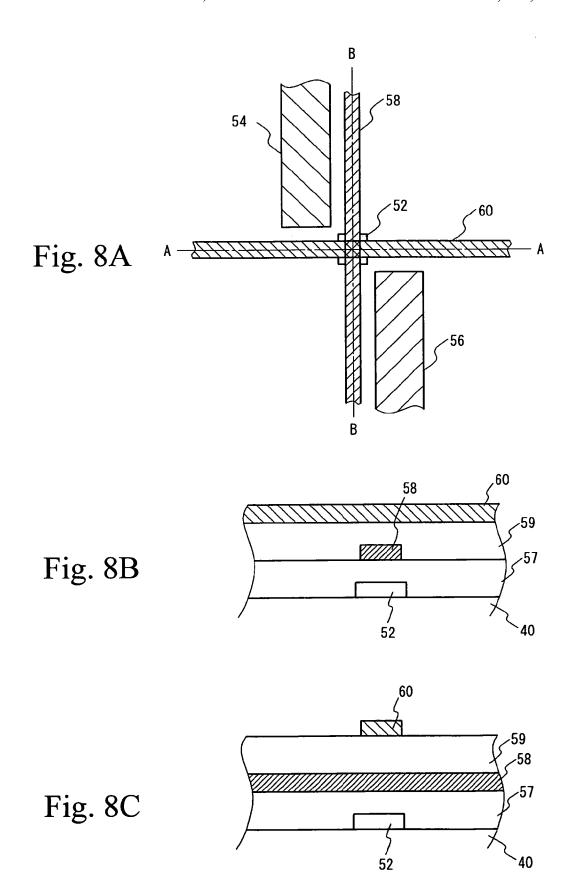

- FIG. **8**A is a top view illustrating the mechanism of changing the magnetization arrangement of a single-electron spin transistor (SEST) to be used in the first through fourth embodiments;

- FIG. 8B is a cross-sectional view of the structure, taken along the line A-A of FIG. 8A;

- FIG. **8**C is a cross-sectional view of the structure, taken along the line B-B of FIG. **8**A;

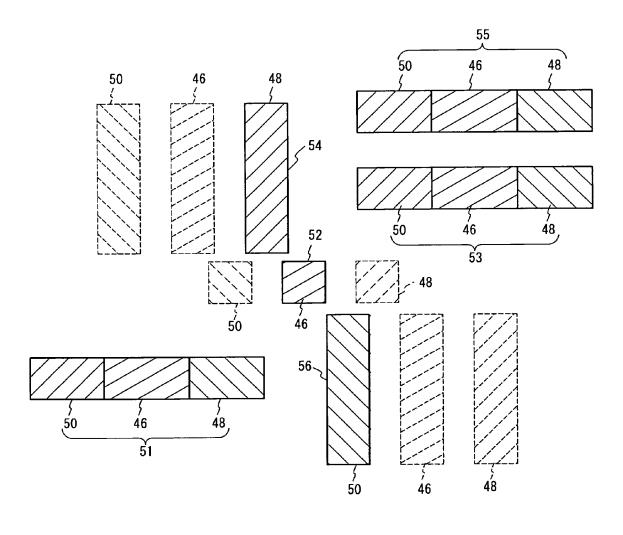

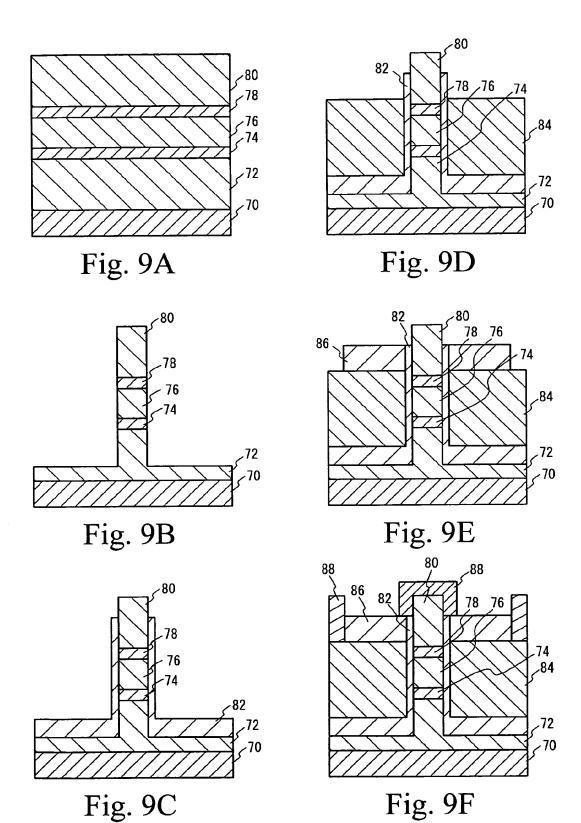

- FIGS. 9A through 9F are cross-sectional views illustrating another example structure of a single-electron spin transistor (SEST) and a method for manufacturing the single-electron spin transistor;

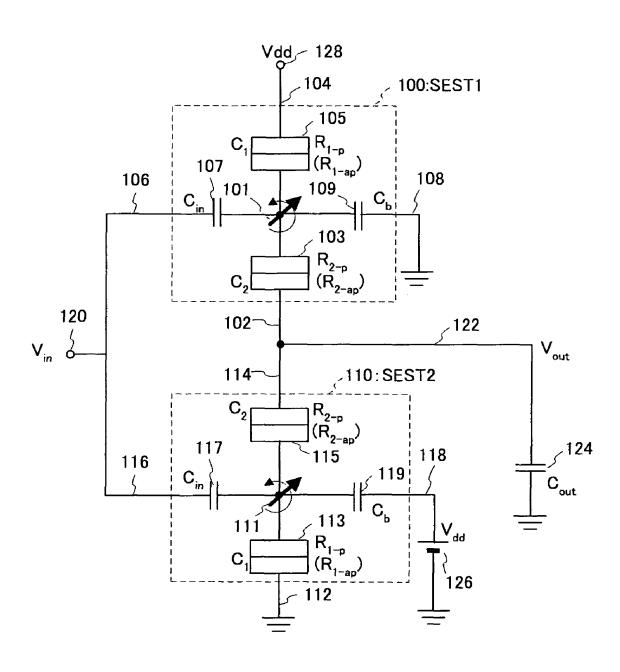

- FIG. 10 is a circuit diagram of an inverter circuit in accordance with a first embodiment;

- FIG. 11 is a circuit diagram showing the resistance values, the capacitance values and the voltage values used in a simulation of the input/output characteristics of the inverter circuit in accordance with the first embodiment;

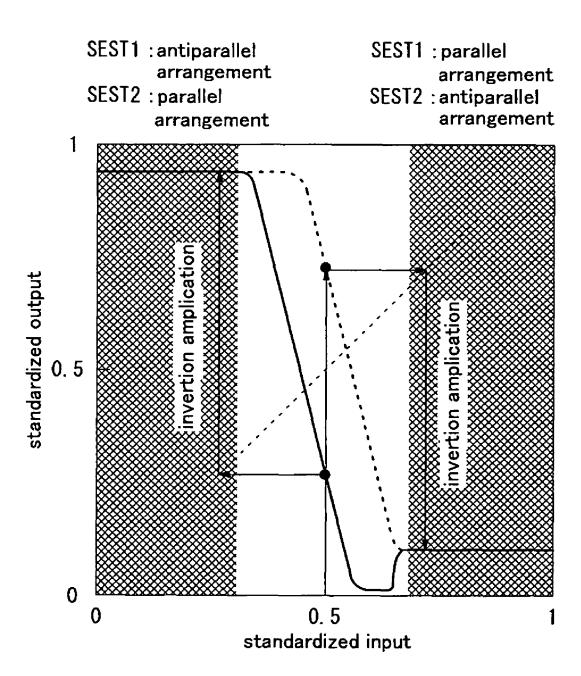

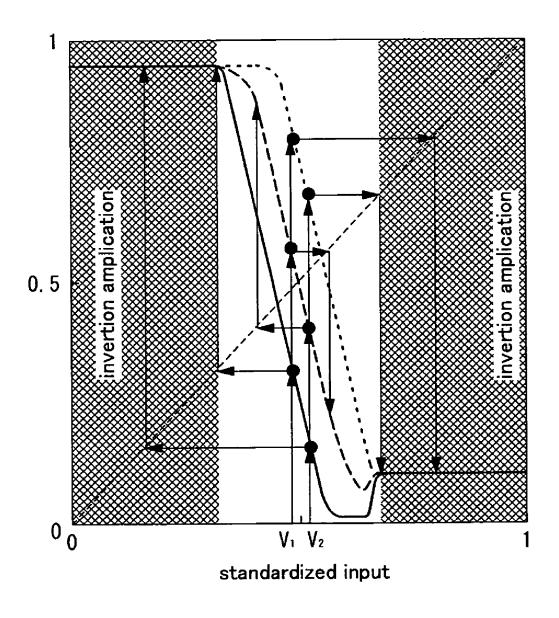

- FIG. 12 shows the results of the simulation of the input/ output characteristics of the inverter circuit in accordance with the first embodiment;

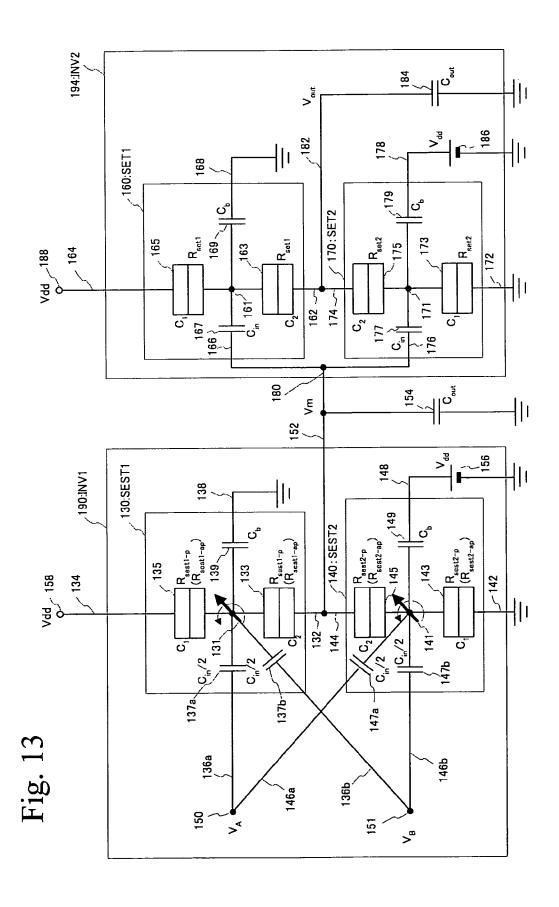

- FIG. 13 is a circuit diagram of a logic circuit in accordance with a second embodiment;

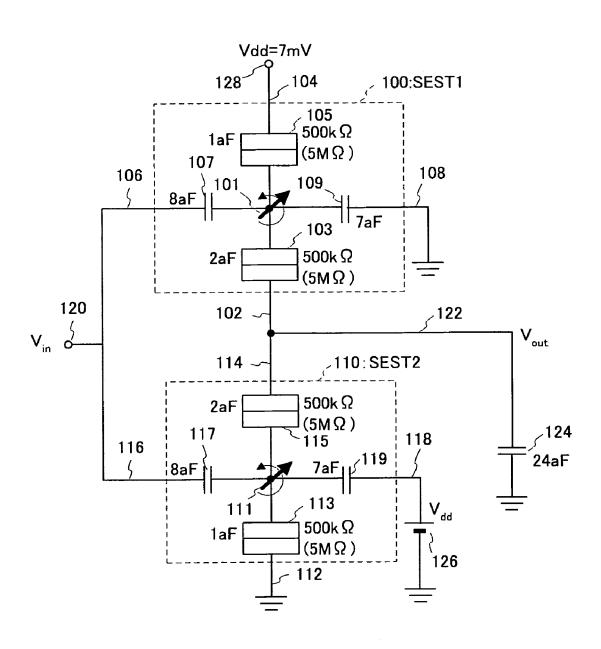

- FIG. 14 is a circuit diagram showing the resistance values, the capacitance values and the voltage values used in simulations of the outputs of the logic circuit in accordance with the second embodiment;

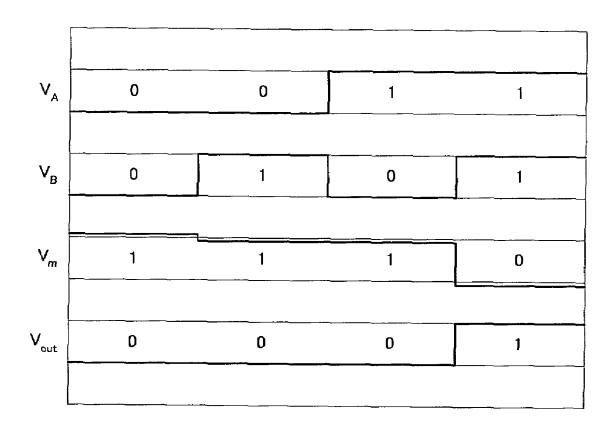

- FIG. 15 shows the results of the simulation of the output of the AND function of the logic circuit in accordance with the second embodiment:

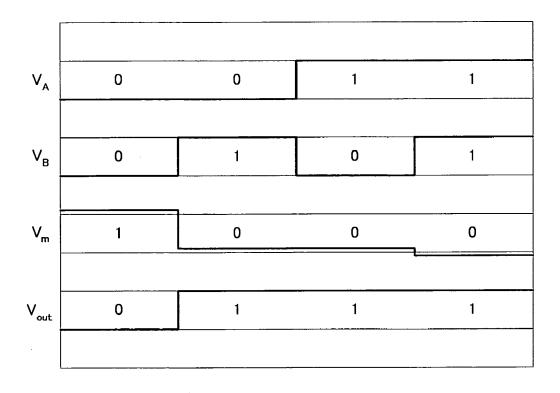

- FIG. 16 shows the results of the simulation of the output of the OR function of the logic circuit in accordance with the second embodiment;

- FIG. 17 shows the results of a simulation performed on the input/output characteristics of the inverter circuit of the first embodiment, with the input/output characteristics of a case where SEST1 and SEST2 both have the parallel arrangement being added;

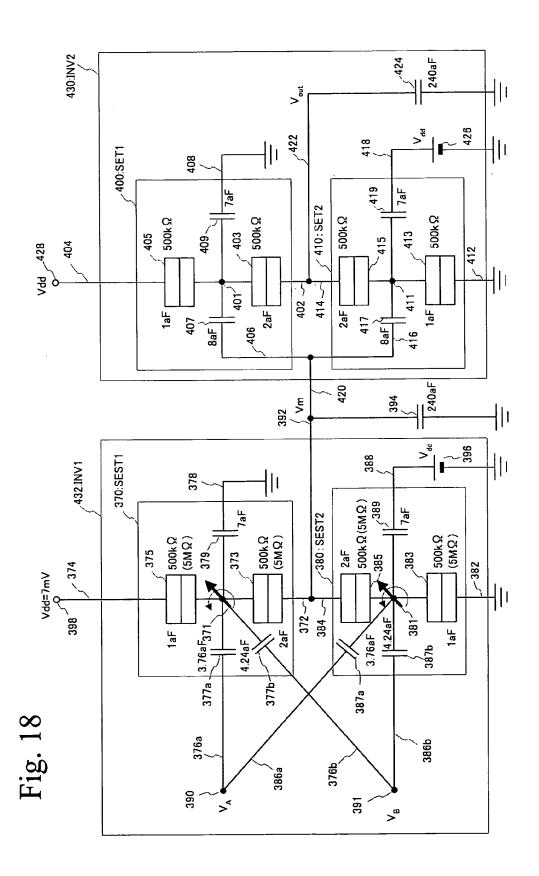

- FIG. 18 is a circuit diagram showing the resistance values, the capacitance values and the voltage values used in simulations of the outputs of a logic circuit in accordance with a third embodiment;

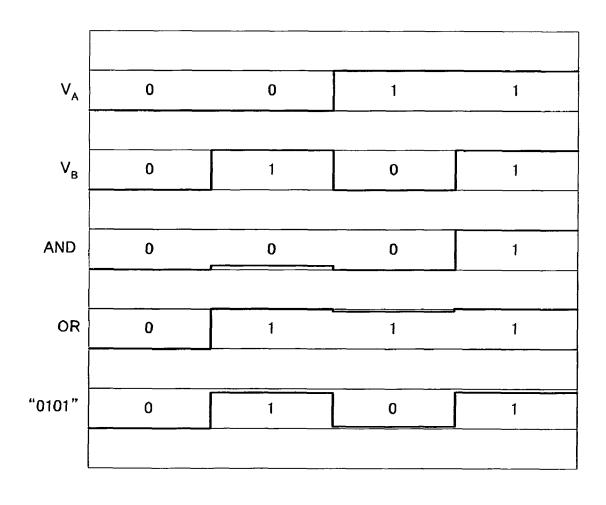

- FIG. 19 shows the results of simulations performed on the outputs of an AND function, the OR function, and the "0101" function of the logic circuit in accordance with the third embodiment;

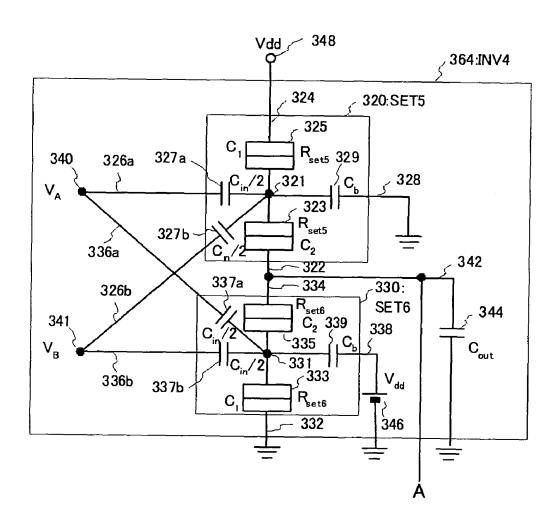

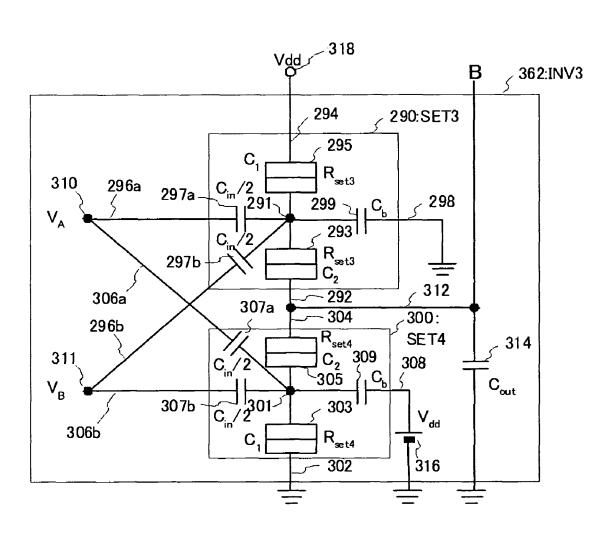

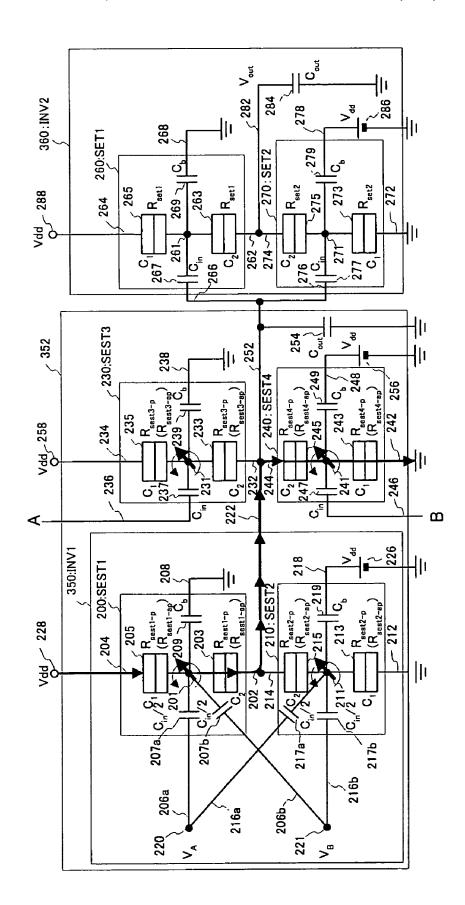

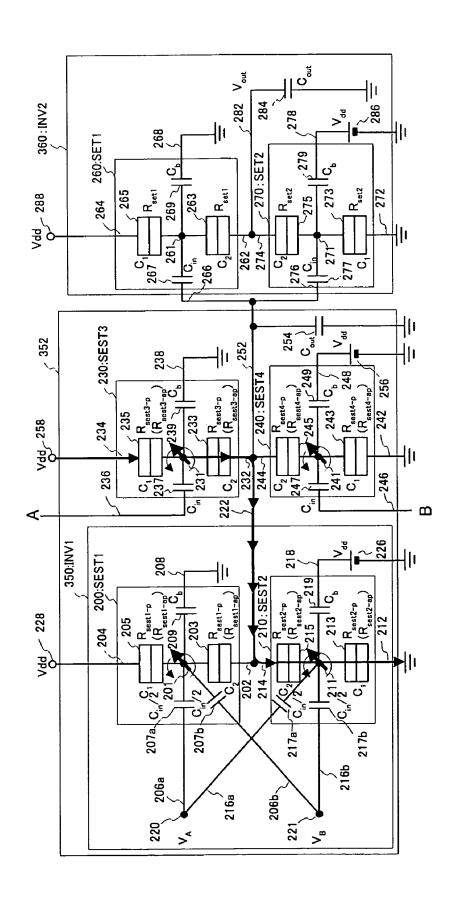

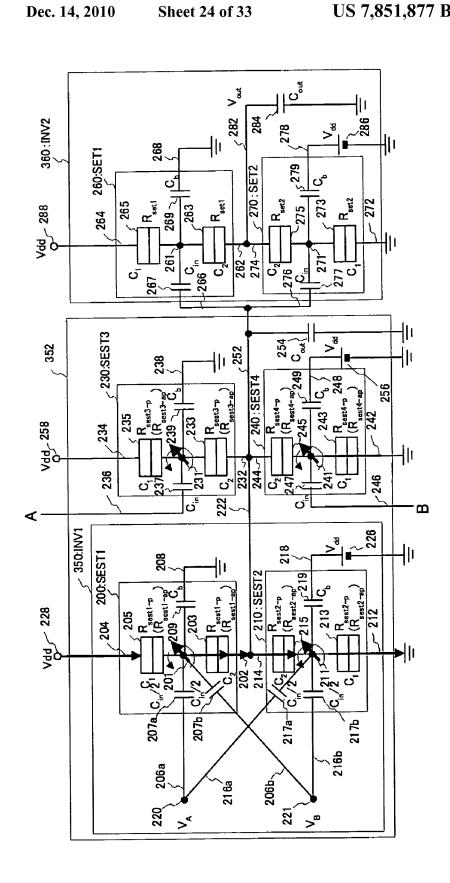

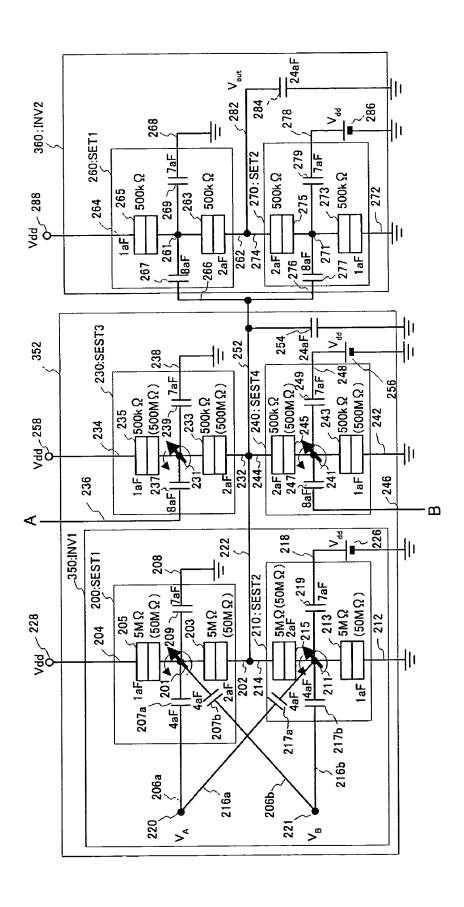

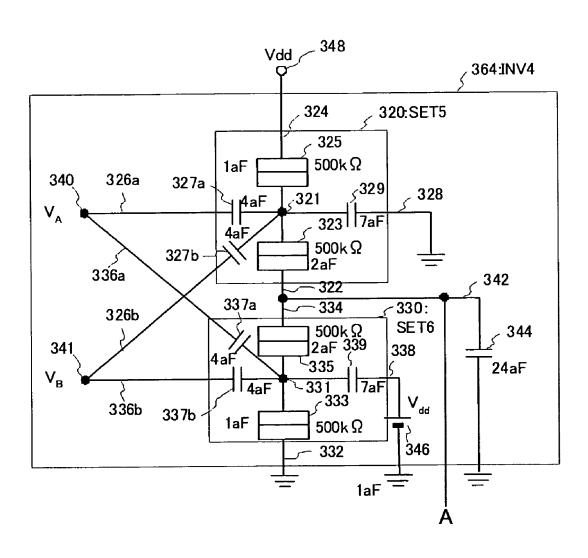

- FIG. 20 is a circuit diagram (1) of a logic circuit in accordance with a fourth embodiment, where the line A is connected to the line A of FIG. 21, and the line B is connected to the line B of FIG. 22;

- FIG. 21 is a circuit diagram (2) of the logic circuit in accordance with the fourth embodiment, where the line A is connected to the line A of FIG. 20;

- FIG. 22 is a circuit diagram (3) of the logic circuit in accordance with the fourth embodiment, where the line B is connected to the line B of FIG. 20;

FIG. 23 is a circuit diagram for explaining an operation to be performed in a case where "0" is input to the logic circuit in accordance with the fourth embodiment;

FIG. **24** is a circuit diagram for explaining an operation to be performed in a case where "1" is input to the logic circuit 5 in accordance with the fourth embodiment;

FIG. 25 is a circuit diagram for explaining an operation to be performed in a case where "0.5" is input to the logic circuit in accordance with the fourth embodiment;

FIG. **26** is a circuit diagram (1) showing the resistance 10 values, the capacitance values, and the voltage values used in simulations of the outputs of the logic circuit in accordance with the fourth embodiment, where the line A is connected to the line A of FIG. **27**, and the line B is connected to the line B of FIG. **28**;

FIG. 27 is a circuit diagram (2) showing the resistance values, the capacitance values, and the voltage values used in the simulations of the outputs of the logic circuit in accordance with the fourth embodiment, where the line A is connected to the line A of FIG. 26;

FIG. 28 is a circuit diagram (3) showing the resistance values, the capacitance values, and the voltage values used in the simulations of the outputs of the logic circuit in accordance with the fourth embodiment, where the line B is connected to the line B of FIG. 26;

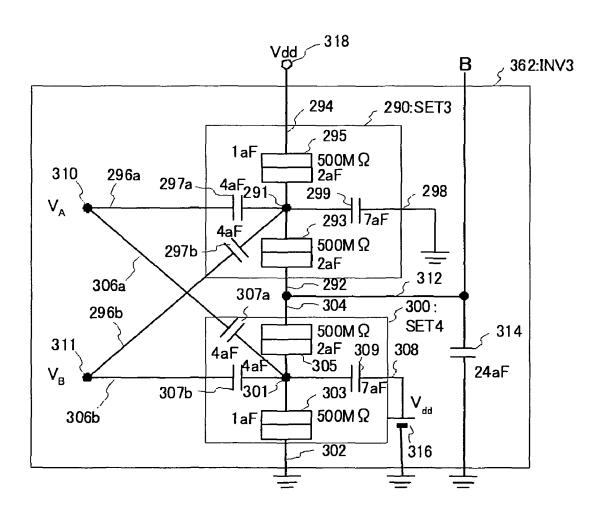

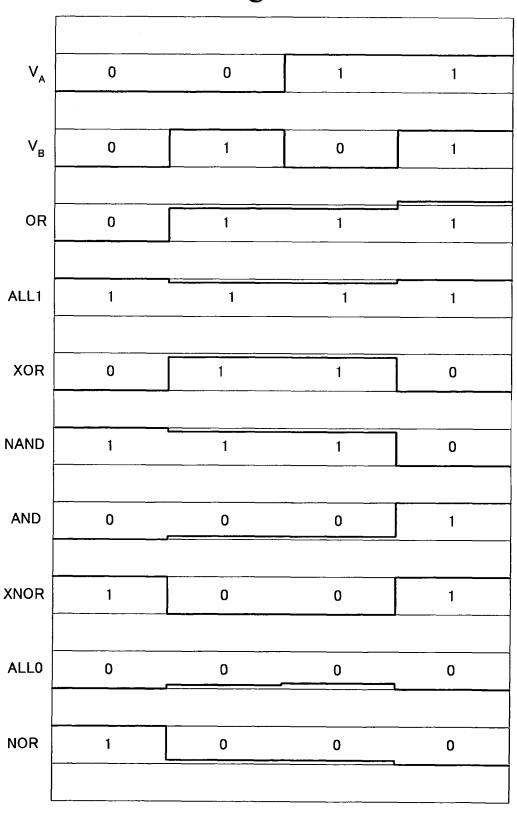

FIG. 29 shows the results of simulations performed on the outputs of all the symmetric Boolean functions of the logic circuit in accordance with the fourth embodiment;

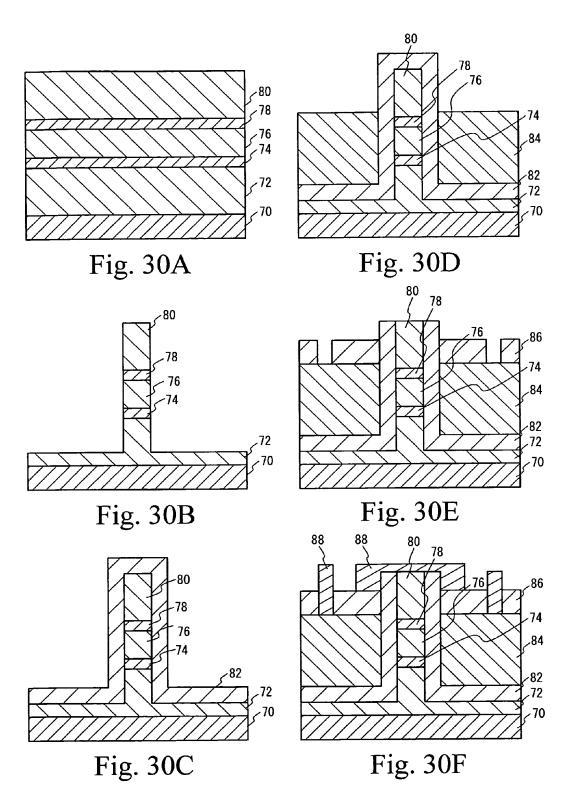

FIGS. **30**A through **30**F are cross-sectional views illustrating the method for manufacturing a SEST in accordance with 30 a fifth embodiment;

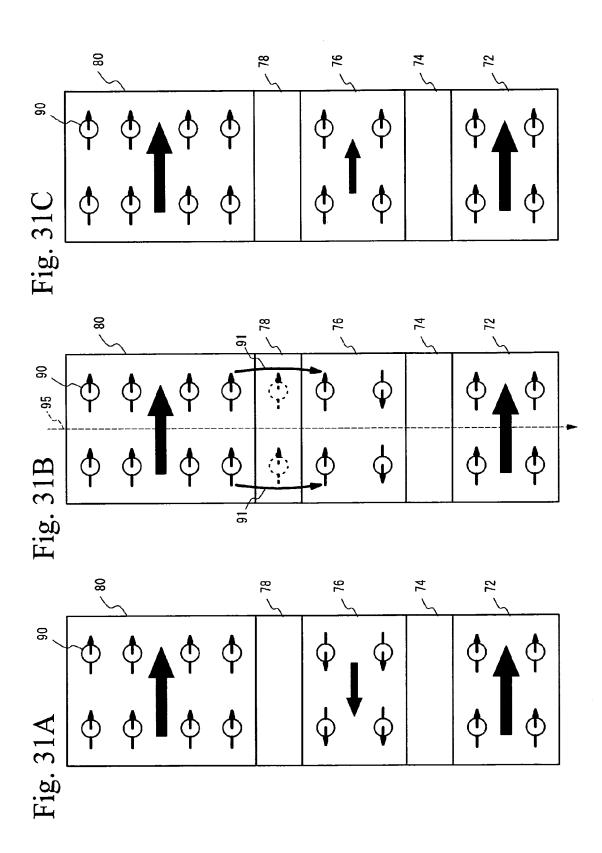

FIGS. 31A through 31C are cross-sectional views (1) illustrating the method of changing the magnetization arrangement of the island of the SEST in accordance with the fifth embodiment;

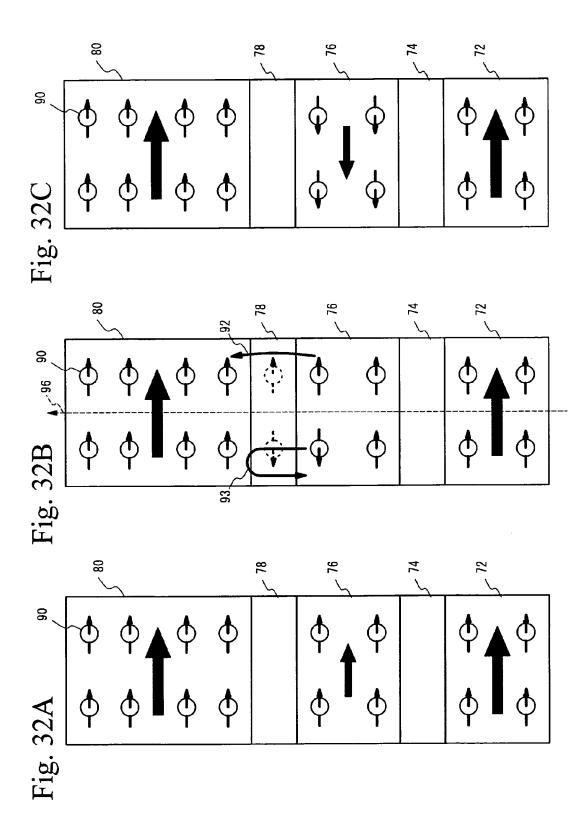

FIGS. 32A through 32C are cross-sectional views (2) illustrating the method of changing the magnetization arrangement of the island of the SEST in accordance with the fifth embodiment;

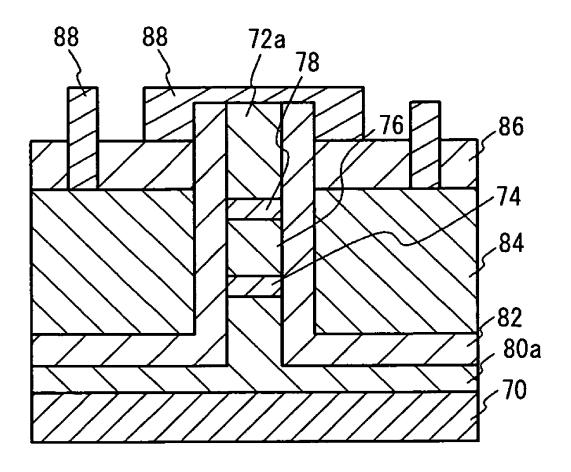

FIG. 33 is a cross-sectional view of a SEST in accordance 40 with a modification of the fifth embodiment; and

FIGS. **34**A and **34**B illustrate the method of varying the magnetization intensity of the island of a SEST in accordance with a sixth embodiment.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

First, a single-electron spin transistor (hereinafter referred to as a SEST) that is a component of the present invention is 50 described.

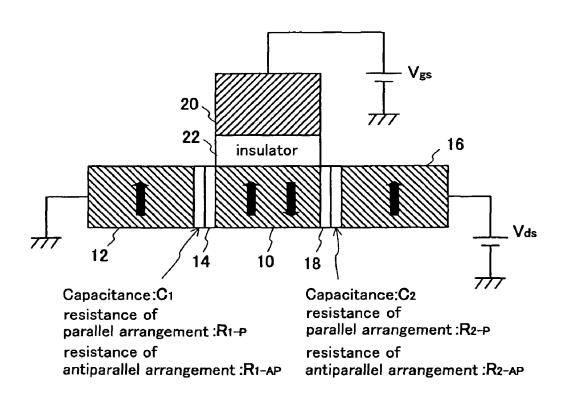

FIG. 1 is a schematic view of a SEST. A SEST is a singleelectron transistor (hereinafter referred to as a SET) using ferromagnetic material. First, a SET that does not include a ferromagnetic material is described. A SET includes a source 55 12, a drain 16, an island 10 that is provided between the source 12 and the drain 16 and has tunnel junctions 14 and 18 between the island 10 and the source 12 and the drain 16, respectively, and a gate 20 that is connected to the island 10 via a gate capacitance (capacitance value Cg) formed with an 60 insulating film 22 (or a space). Here, the tunnel functions 14 and 18 are formed with insulating films of approximately 2 nm, for example, and have capacitance values  $C_1$  and  $C_2$ , respectively. As the cross section and film thickness of each of the tunnel junctions 14 and 18 of the SET are very small, the 65 capacitance values  $C_1$  and  $C_2$  can be made very small. With this arrangement, the electrons in the island 10 can be con10

trolled one by one by the capacitance gate **20**. Accordingly, the power consumption can be made very small. Also, since a very small island is used, the area of the transistor can also be made very small.

A SEST can be realized by making at least one of the source 12, the drain 16, and the island 10 of the SET contain a ferromagnetic material with reversible magnetization. An example case where the source 12 and the drain 16 include ferromagnetic materials magnetized in the same direction, and the island 10 includes a ferromagnetic material having a variable magnetization direction, as shown in FIG. 1, is described. Where the island 10 is magnetized in the same direction as the magnetization direction of the source 12 and the drain 16 (parallel arrangement), the resistance values  $R_{1-p}$ and  $R_{2-p}$  of the tunnel junctions 14 and 18 can be made smaller by the tunnel magnetoresistance effect. Where the island 10 is magnetized in the opposite direction from the magnetization direction of the source 12 and the drain 16 (antiparallel arrangement), the resistance values  $R_{1-ap}$  and 20  $R_{2-ap}$  of the tunnel junctions 14 and 18 can be made larger by the tunnel magnetoresistance effect. By varying the magnetization direction of the ferromagnetic material having a variable magnetization direction in this manner, the conductance between the source 12 and the drain 16 can be controlled in a nonvolatile fashion.

In a different structure from the above, the conductance between the source and the drain can be controlled by making one of the island 10, the source 12, and the drain 16 include a ferromagnetic material having a fixed magnetization direction, making one of the others include a ferromagnetic material having a variable magnetization direction, and changing the magnetization direction of the ferromagnetic material having a variable magnetization direction.

In the structure in which the source 12 and the drain 16 include ferromagnetic materials magnetized in the same direction, and the island 10 include a ferromagnetic material having a variable magnetization direction, the resistance values of the tunnel junctions 14 and 18 can be changed by varying the magnetization direction. Accordingly, the conductance can be certainly controlled by varying the magnetization direction of the island, and the function of a logic circuit is reconfigured. Thus, a preferred transistor structure can be realized.

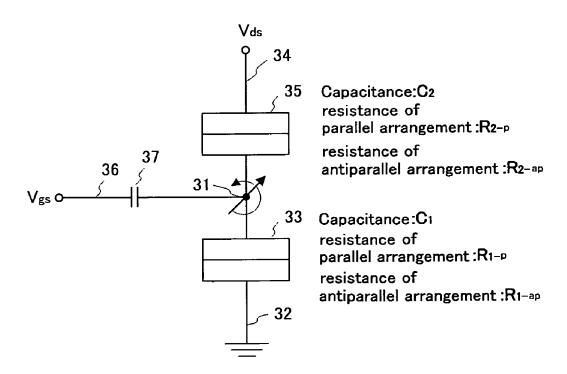

FIG. 2 shows the circuit symbols of the SEST of FIG. 1.

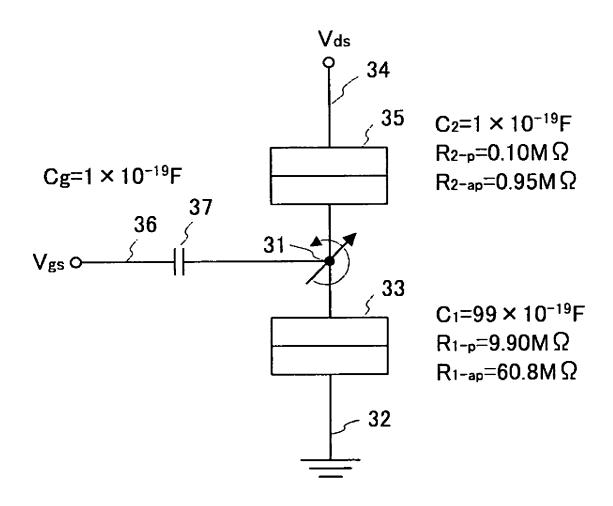

Reference numeral 31 indicates the island, reference numeral 32 indicates the source, reference numeral 33 indicates the tunnel junction having the capacitance value C<sub>1</sub>, the resistance value R<sub>1-p</sub> in the parallel arrangement, and the resistance value R<sub>1-ap</sub> in the antiparallel arrangement, reference numeral 34 indicates the drain, the reference numeral 35 indicates the tunnel junction having the capacitance value C<sub>2</sub>, the resistance value R<sub>2-p</sub> in the parallel arrangement, and the resistance value R<sub>2-ap</sub> in the antiparallel arrangement, reference numeral 36 indicates the gate, and reference numeral 37 indicates the gate capacitance having the capacitance value C<sub>2</sub>.

$C_g$ . For example,  $C_g$  is  $1\times10^{-19}$  F,  $C_1$ ,  $R_{1-p}$ , and  $R_{1-ap}$  are  $99\times10^{-19}$  F, 9.9 MΩ, 60.8 MΩ, respectively, and  $C_2$ ,  $R_{2-p}$ , and  $R_{2-ap}$  are  $1\times^{-19}$  F, 0.1 MΩ, 0.95 MΩ, respectively, as shown in FIG. 3. FIGS. 4 and 5 show the current-voltage characteristics as the results of simulations performed with those values.

FIG. 4 shows the drain current  $I_{ds}$ -drain voltage  $V_{ds}$  characteristics observed where the gate voltage is 0 V, and the temperature is 0.92 K. In FIG. 4, the solid line indicates the drain current in the case of parallel arrangement, and the broken line indicates the drain current in the case of the antiparallel arrangement. When the drain voltage  $V_{ds}$  is equal

to or lower than the Coulomb threshold value ( $V_{Cth}$ ), There is not a current flowing. This is because electron tunneling is prohibited by a Coulomb blockade effect. The stepwise increase in drain current caused by the application of a drain voltage shows that the number of electrons flowing in the 5 island 10 increases one by one. In the case of the parallel arrangement, the drain current is higher and the conductance is smaller than in the case of the antiparallel arrangement. In this manner, the magnetization direction (the magnetization arrangement) is switched between the parallel arrangement and the antiparallel arrangement, the conductance between the source 32 and the drain 34 can be controlled. The magnetization direction is maintained until the next change in the magnetization direction. Thus, the conductance can be controlled in a nonvolatile fashion.

FIG. 5 shows the drain current  $I_{ds}$ -gate voltage  $V_{gs}$  characteristics observed where the drain voltage is  $V_{Cth}$ , and the temperature is 0.92 K. Due to a Coulomb blockade effect, a drain current appears periodically. By adjusting the gate voltage (or the control gate voltage) and the gate capacitance (or the control gate capacitance) in this manner, the current flowing state can be switched between a state in which a drain current flows and a state in which a drain current does not flow. As in FIG. 4, in the case of the parallel arrangement, the drain current is higher than in the case of antiparallel arrange- 25 ment.

Referring now to FIG. **6**, an example of a method for manufacturing a SEST is described. FIG. **6** is a cross-sectional view showing a step during the manufacturing process. For example, a lower-layer resist **42** and an upper-layer resist **44** are applied as two-layer resists onto an insulator substrate **40**, and a predetermined pattern is formed with an electron beam exposure device. Iron or cobalt as a ferromagnetic material is deposited onto the middle of the substrate from the direction denoted by A in FIG. **6**, so as to form regions **46**. 35 After that, a 2-nm insulating film to be the tunnel junctions is formed. Further, irons or cobalt, for example, is deposited from the directions denoted by B and C, so as to form regions **48** and regions **50**.

In the above manner, the pattern shown in the top view of 40 FIG. 7 is completed. In FIG. 7, the regions 46, 48, and 50 that do not constitute the SEST are indicated by broken lines. Those regions indicated by the broken lines are removed by etching. An island 52 formed with a region 46, a source 54 formed with a region 48, and a drain 56 formed with a region 45 50 are formed on the substrate 40. Insulating films (not shown) to be the tunnel junctions are formed between the island 52 and the source 54 and between the island 52 and the drain 56. Further, a first gate 51, a second gate 53, and a control gate 55 are formed on the substrate 40. In this struc- 50 ture, the source 54, the drain 56, and the gates 51, 53, and 55 are formed on the sides of the island 52. Here, the portions between the island 52 and the gates 51, 53, and 55 may be covered with insulating films, or may be hollows. In this manner, the gates 51, 53, and 55 are capacitively coupled to 55 the island 52 via the space formed by the insulating films or hollows existing between the island 52 and the gates 51, 53, and 55. The capacitance of the space formed by the insulating films or hollows is the gate capacitance (or the control gate capacitance).

As the island **52** can be made very small, the SEST having the above structure can have very small gate capacitance. Accordingly, an analog input can be realized with a very small area. The gate may be formed on the island via an insulating film, or under the substrate **40** through the substrate **40**. In 65 either case, a gate capacitively coupled to the island can be formed.

12

FIGS. 8A through 8C illustrate an example of the mechanism of varying the magnetization direction (the magnetization arrangement) of the island. FIG. 8A is a top view. FIG. 8B is a cross-sectional view, taken along the line A-A of FIG. 8A. FIG. 8C is a cross-sectional view, taken along the line B-B of FIG. 8A. In FIG. 8A, the island 52, the source 54, and the drain 56 are arranged in the same manner as in FIG. 7. As shown in FIGS. 8B and 8C, an interlayer insulating film 57, a wire 58, an interlayer insulating film 59, and a wire 60 are formed on a transistor. The wire 58 and the wire 60 cross each other on the island 52. By applying a pulse current to the wire 50 and the wire 60, a magnetic field is induced in the island 52, and the magnetization direction (the magnetization arrangement) of the island 52 can be varied.

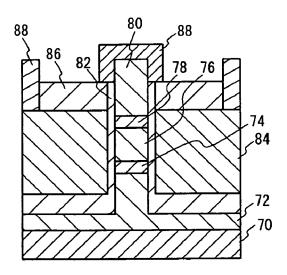

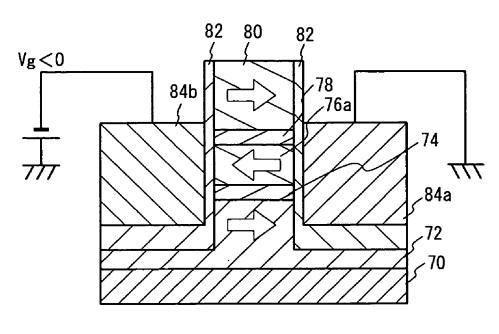

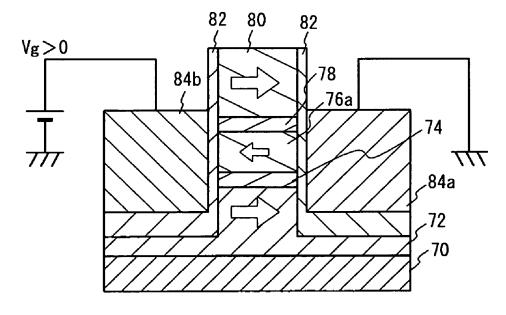

Referring now to FIGS. 9A through 9F, another example structure of a SEST and a method for manufacturing the SEST are described. As shown in FIG. 9A, an iron (Fe) film as a source 72, a magnesium oxide (MgO) film as a tunnel junction 74, an iron (Fe) film as an island 76, a magnesium oxide (MgO) film as a tunnel junction 78, and an iron (Fe) film as a drain 80 are stacked to form a hetero structure on a magnesium oxide (MgO) substrate 70 by MBE, for example. Etching is then performed as deep as the source 72 of the stacked films, except for a predetermined region, by electron beam exposure and the ion milling technique. In this manner, a pillar structure is formed (FIG. 9B). An insulating film 82 to form a gate capacitance is formed with a silicon nitride film by plasma CVD (FIG. 9C). A gate 84 is formed with aluminum (Al) by a deposition technique (FIG. 9D). A silicon nitride film 86 is formed by plasma CVD, so as to form contact holes in predetermined regions (FIG. 9E). A wiring layer 88 is formed with aluminum (Al) by a deposition technique (FIG. 9F).

In the above described manner, the source 72, the island 76, and the drain 80 are stacked on the substrate 70, and the gate 84 is formed on a side of the island 76. The gate 84 is capacitively coupled to the island 76 via the space formed by the insulating film existing between the island 76 and the gate 84. In this case, the silicon nitride film 82 between the island 76 and the gate 84 serves as the gate capacitance. As the island 76 is very thin, the gate capacitance can be made very small. Accordingly, an analog input can be realized with a very small area. In this manner, a SEST having the source 72, the island 76, and the drain 80 that include a ferromagnetic material can be formed.

As described above, each SEST deals with a single electron, and the power consumption of the transistor is small. Accordingly, the area of the transistor can be made small. Furthermore, as each SEST deals with one or two electrons flowing through the island, the charge amount to be controlled is small. By connecting the gate capacitively coupled to the island to an input terminal, an analog input to a logic circuit can be realized. More specifically, analog inputs from input terminals to SESTs are weighted with the gate capacitance connected from each input terminal to the gate of each SEST, so as to realize an analog input to the logic circuit. Accordingly, a large-area floating gate that has been required conventionally becomes unnecessary. Thus, the circuit area of the logic circuit including SESTs can be made very small. As described with reference to FIG. 7 and FIGS. 9A through 9F, in a SEST, the gate capacitance of the gate capacitively

coupled to the island can be made very small, and the circuit area can be further reduced accordingly.

#### First Embodiment

A first embodiment is an example of an inverter circuit that can control the logic threshold value in a nonvolatile manner, by varying the variable magnetization direction of each SEST.

FIG. 10 shows a circuit diagram of the inverter circuit in 10 accordance with the first embodiment. This inverter circuit (the first inverter circuit) includes a SEST1 (100) and a SEST2 (110). The source 102 of the SEST1 (100) is connected to an output terminal 122, and the drain 104 is connected to a first power supply terminal 128. Tunnel junctions 103 and 105 are provided between an island 101 and the source 102 and between the island 101 and the drain 104, respectively. The tunnel junctions 103 and 105 have capacitance values  $C_2$  and  $C_1$ , resistance values  $R_{2-p}$  and  $R_{1-p}$  in the parallel arrangement, and resistance values  $R_{2-ap}$  and  $R_{1-ap}$  in 20 the antiparallel arrangement. A gate 106 is connected to an input terminal 120. A control gate 108 is grounded. The capacitance value of a gate capacitance 107 between the island 101 and the gate 106 is  $C_{in}$ , and the capacitance value of a control gate capacitance 109 between the island 101 and  $_{25}$ the control gate 108 is  $C_b$ .

The source 112 of the SEST2 (110) is grounded (or connected to the second power supply terminal), and the drain 114 is connected to the output terminal 122. Tunnel junctions 113 and 115 are provided between an island 111 and the 30 source 112 and between the island 111 and the drain 114, respectively. The tunnel junctions 113 and 115 have capacitance values  $C_1$  and  $C_2$ , resistance values  $C_{1-p}$  and  $C_{2-p}$  in the parallel arrangement, and resistance values  $C_{1-p}$  and  $C_{2-p}$  in the antiparallel arrangement. A gate 116 is connected to the 35 input terminal 120. A control gate 118 is connected to a power supply  $V_{dd}$  126. The capacitance value of a gate capacitance 117 between the island 111 and the gate 116 is  $C_{ip}$ , and the capacitance value of a control gate capacitance 119 between the island 111 and the control gate 118 is  $C_b$ . The output 40 terminal 122 is grounded via a capacitance 124.

The function of this inverter is now described. The SEST1 (100) is switched on when an input  $V_{in}$  of the input terminal 120 is "0" (low level), and is switched off when the input  $V_{in}$  of the input terminal 120 is "1" (high level). The SEST2 (110)  $_{45}$  is switched off when the input terminal 120 is "0", and is switched on when the input terminal 120 is "1". The following is the reason that the SEST1 (100) and the SEST2 (110) operate in the opposite manners. Different voltages (ground and  $V_{dd}$ ) are applied to the control gates 108 and 118 of the respective SESTs. With those voltages, the SEST1 (100) and the SEST2 (110) have different Coulomb threshold voltages so as to perform the opposite operations.

A simulation was performed on the input/output characteristics of the first embodiment. FIG. 11 shows the capacitance 55 values, the resistance values, and the voltages used in the simulation. The capacitance unit aF represents  $1\times10^{-18}$  F. FIG. 12 shows the results of the input/output characteristics simulation. In FIG. 12, the abscissa axis indicates standardized inputs, and the ordinate axis indicates standardized outputs. The hatching portions indicate the ranges in which the low level "0" or the high level "1" is output in response to a standardized input.

Since the SEST1 (100) is switched on and the SEST2 (110) is switched off in the neighborhood of the point at which the input  $V_{in}$  of the input terminal 120 is "0", an output  $V_{out}$  of the output terminal 122 becomes high level, which is "1". Mean-

14

while, since the SEST1 (100) is switched off and the SEST2 (110) is switched on in the neighborhood of the point at which the input  $V_{in}$  of the input terminal 120 is "1", the output  $V_{out}$  of the output terminal 122 becomes low level, which is "0".

The SEST1 (100) and the SEST2 (110) are switched on in the vicinity of the point at which the  $V_{in}$  is "0.5". Here, the output Vout is determined by the resistance values of the tunnel junctions 103 and 105 of the SEST1 (100) and the tunnel junctions 113 and 115 of the SEST2 (110). If the resistance value of the tunnel junctions 103 and 105 of the SEST1 (100) is larger than the resistance value of the tunnel junctions 113 and 115 of the SEST2 (110), the output  $V_{out}$  is almost "0". This can be achieved where the magnetization arrangement of the SEST1 (100) is the antiparallel arrangement while the magnetization arrangement of the SEST2 (110) is the parallel arrangement. The input/output curve of this case is indicated by the solid line in FIG. 12. The standardized output is approximately "0.25". An inverter circuit having an A-D converter function is provided in the next stage, so as to perform inverting amplification. In this manner, the high level "1" can be output (as indicated by the arrow extending leftward from the solid line and then extending upward in FIG. 12).

If the resistance value of the tunnel junctions 103 and 105 of the SEST1 (100) is smaller than the resistance value of the tunnel junctions 113 and 115 of the SEST2 (110), the output  $V_{out}$  is almost "1". This can be achieved where the magnetization arrangement of the SEST1 (100) is the parallel arrangement while the magnetization arrangement of the SEST2 (110) is the antiparallel arrangement. The input/output curve of this case is indicated by the dotted line in FIG. 12. The standardized output is approximately "0.75". An inverter circuit having an A-D converter function is also provided in the next stage, so as to perform inverting amplification. In this manner, the low level "0" can be output (as indicated by the arrow extending rightward from the dotted line and then extending downward in FIG. 12).

By varying the magnetization direction of each SEST in the above manner, the logic threshold value of the inverter circuit can be changed. Accordingly, the output  $V_{out}$  of the output terminal 122 can be adjusted to almost "0" or "1", where the input  $V_{in}$  of the input terminal 120 is "0.5". As described above, in accordance with the first embodiment, the logic threshold value can be controlled by varying the magnetization direction, as in the conventional technique 1. More specifically, the logic threshold value can be controlled in a nonvolatile manner by varying the magnetization directions of ferromagnetic islands having a variable magnetization direction. In other words, the function of a logic circuit can be reconfigured in a nonvolatile manner.

As described above, in accordance with the first embodiment, the logic threshold value of an inverter circuit can be controlled in a nonvolatile manner by varying the magnetization direction of ferromagnetic islands having a variable magnetization direction. Furthermore, as SESTs are used as transistors, the power consumption and area of each transistor can be made smaller, and the power consumption and circuit area of the logic circuit can be made smaller, accordingly.

## Second Embodiment

A second embodiment is an example of a logic circuit that can reconfigure an OR/AND circuit function using SESTs in a nonvolatile manner. FIG. 13 is a circuit diagram of the logic circuit in accordance with the second embodiment. This logic circuit includes a first inverter circuit (INV1) 190 and a second inverter circuit (INV2) 194. The first inverter circuit

(INV1) 190 includes a SEST1 (130) and a SEST2 (140). The INV1 (190) has the same circuit structure and functions as the inverter circuit of the first embodiment, except that a first input terminal and a second input terminal are provided, and an analog input is to be input.

The structure of the logic circuit is now described in greater detail. The source 132 of the SEST1 (130) is connected to an output terminal 152 of the INV1 (190), and the drain 134 is connected to a first power supply terminal 158. Tunnel junctions 133 and 135 are provided between an island 131 and the source 132 and between the island 131 and the drain 134, respectively. The tunnel junctions 133 and 135 have capacitance values  $C_2$  and  $C_1$ , a resistance value  $R_{sest1-p}$  in the parallel arrangement, and a resistance value  $R_{sest1-ap}$  in the antiparallel arrangement. A first gate 136a is connected to the first input terminal 150, and a second gate 136b is connected to the second input terminal 151. A control gate 138 is grounded. The capacitance values of a first gate capacitance 137a between the island 131 and the first gate 136a, and a second gate capacitance 137b between the island 131 and the second gate 136b are  $C_{in}/2$ . The capacitance value of a control gate capacitance 139 between the island 131 and the control gate 138 is  $C_b$ .

The source 142 of the SEST2 (140) is grounded (or connected to the second power supply terminal), and the drain 144 is connected to the output terminal 152 of the INV1 (190). Tunnel junctions 143 and 145 are provided between an island 141 and the source 142 and between the island 141 and the drain 144, respectively. The tunnel junctions 143 and 145 have capacitance values  $C_1$  and  $C_2$ , a resistance value  $R_{sest2-p}$ in the parallel arrangement, and a resistance values  $R_{sest2-ap}$  in the antiparallel arrangement. A first gate **146***a* is connected to the first input terminal 150, and a second gate 146b is connected to the second input terminal 151. A control gate 148 is connected to a power supply  $V_{\it dd}$  156. The capacitance values of a first gate capacitance 147a between the island 141 and the first gate **146***a*, and a second gate capacitance **147***b* between the island 141 and the second gate 146b are  $C_{in}/2$ . The output terminal 152 is grounded via a capacitance 154.

Further, the output terminal 152 of the INV1 (190) is connected to an input terminal 180 of the second inverter circuit (INV2) 194. The INV2 (194) is a Tucker-type inverter circuit, and includes a SET1 (160) and a SET2 (170) that are two single-electron transistors (SET). The source 162 of the SET1 45 (160) is connected to an output terminal 182, and the drain 164 is connected to a power supply  $V_{dd}$  188. Tunnel junctions 163 and 165 are provided between an island 161 and the source 162 and between the island 161 and the drain 164, respectively. The tunnel junctions 163 and 165 have capaci- 50 190. tance values  $C_2$  and  $C_1$ , and a resistance value  $R_{\mathit{set1}}$ . A gate 166 is connected to the output terminal 152 of the INV1 (190). A control gate 168 is grounded. The capacitance value of a gate capacitance 167 between the island 161 and the gate **166** is  $C_{in}$ . The capacitance value of a control gate capacitance  $_{55}$ **169** between the island **161** and the control gate **168** is  $C_b$ .

The source 172 of the SET2 (170) is grounded, and the drain 174 is connected to the output terminal 182. Tunnel junctions 173 and 175 are provided between an island 171 and the source 172 and between the island 171 and the drain 174, 60 respectively. The tunnel junctions 173 and 175 have capacitance values  $C_1$  and  $C_2$ , and a resistance value  $R_{set2}$ . A gate 176 is connected to the output terminal 152 of the INV1 (190). A control gate 178 is connected to a power supply  $V_{dd}$  186. The capacitance value of a gate capacitance 177 between 65 the island 171 and the gate 176 is  $C_{in}$ . The output terminal 182 is grounded via a capacitance 184.

16

In the logic circuit in accordance with the second embodiment, the first input terminal **150** is capacitively coupled to the island **131** of the SEST1 (**130**) and the island **141** of the SEST2 (**140**) via the same capacitance value  $C_{in}/2$ , and the second input terminal **151** is also capacitively coupled to the island **131** of the SEST1 (**130**) and the island **141** of the SEST2 (**140**) via the same capacitance value  $C_{in}/2$ .

Accordingly, in the INV1 (190), the capacitance values of the first gate capacitance 137a of the SEST1 (130) and the first gate capacitance 147a of the SEST2 (140) are substantially the same, and the capacitance values of the second gate capacitance 137b of the SEST1 (130) and the second gate capacitance 147b of the SEST2 (140) are substantially the same. Further, the capacitance values of the first gate capacitance 137a of the SEST1 (130) and the first gate capacitance 147a of the SEST2 (140), and the capacitance values of the second gate capacitance 137b of the SEST1 (130) and the second gate capacitance 147b of the SEST2 (140) are substantially the same.

Accordingly, in the INV1 (190), the weights of analog inputs of an input  $V_A$  from the first input terminal 150 to the SEST1 (130) and the SEST2 (140) are substantially the same, and the weights of analog inputs of an input  $V_B$  from the second input terminal 151 to the SEST1 (130) and the SEST2 (140) are substantially the same. Further, the weights of the analog inputs of the input  $V_A$  from the first input terminal 150 to the SEST1 (130) and the SEST2 (140) are substantially the same as the weights of the analog inputs of the input  $V_B$  from the second input terminal 151 to the SEST1 (130) and the SEST2 (140).

Here, the substantially same capacitance values and the substantially same weights are within the range in which an input of approximately "0.5" is input to the INV1 (190). The input of approximately "0.5" is an input within a range in which the logic circuit in accordance with the second embodiment can reconfigure the two-input AND circuit function and the two-input OR circuit function in a nonvolatile manner by varying the magnetization direction of the ferromagnetic material in each SEST having a variable magnetization direction

Table 1 shows a truth table of inputs. Where the input  $V_A$  is "0" and the input  $V_B$  is "0", the input  $V_{in}$  of the INV1 (190) is "0". Where the input  $V_A$  is "0" and the input  $V_B$  is "1", the input  $V_{in}$  of the INV1 (190) is "0.5". Where the input  $V_A$  is "1" and the input  $V_B$  is "0", the input  $V_{in}$  of the INV1 (190) is "0.5". Where the input  $V_A$  is "1" and the input  $V_B$  is "1", the input  $V_{in}$  of the INV1 (190) is "1". In this manner, analog inputs from the first input terminal 150 and the second input terminal 151 can be input to the first inverter circuit (INV1)

TABLE 1

| $V_A$ | $V_B$ | $V_{in}$ |  |

|-------|-------|----------|--|

| "0"   | "0"   | "0"      |  |

| "0"   | "1"   | "0.5"    |  |

| "1"   | "0"   | "0.5"    |  |

| "1"   | "1"   | "1"      |  |

The INV2 (194) has an A-D conversion function, and inverting-amplifies the output  $V_m$  of the INV1 (190). More specifically, the INV2 (194) inverting-amplifies the output of almost "0" or "1" of the INV1 (190) to "1" or "0". Since the INV1 (190) includes SESTs, its output current is very small. Therefore, the second embodiment employs a Tucker-type inverter circuit as the INV2 (194) that includes SETs that can be driven even by a small input current. The INV2 (194) is

driven by an output of an inverter circuit including SETs. It is possible to employ an inverter circuit having a different circuit structure from the above or including other transistors, as long as the inverter circuit has the same functions as the INV2 (194).

Table 2 shows a truth table of the logic circuit in accordance with the second embodiment. Here, the functions observed in a case where the magnetization arrangement of the SEST1 (130) is the parallel arrangement (P) and the magnetization arrangement of the SEST2 (140) is the antiparallel arrangement (AP) are described. Where the input  $V_A$  is "0" and the input  $V_B$  is "0", the output  $V_M$  of the output terminal 152 of the INV1 (190) is "1", and the output  $V_{out}$  of the output terminal 182 of the INV2 (194) is "0". Where the input  $V_A$  is "1" and the input  $V_B$  is "1", the output  $V_M$  is "0", and the output  $V_{out}$  15 is "1". Where the input  $V_A$  is "0" and the input  $V_B$  is "1", or the input  $V_A$  is "1" and the output  $V_{out}$  is almost "1", and the output  $V_{out}$  is almost "0", since the input  $V_M$  is "0.5". In this manner, the logic circuit in accordance with the second embodiment functions as a two-input AND circuit.

TABLE 2

|         |         |                                                            | -          | V <sub>m</sub> |            |                                     |

|---------|---------|------------------------------------------------------------|------------|----------------|------------|-------------------------------------|

| SEST1   | SEST2   | $\begin{matrix} \mathbf{V}_A \\ \mathbf{V}_B \end{matrix}$ | 0          | 0/1<br>1/0     | 1<br>1     | $V_{out}$ (in order of Vm) function |

| AP<br>P | P<br>AP |                                                            | "1"<br>"1" | "0"<br>"1"     | "0"<br>"0" | "0" "1" "1" OR<br>"0" "0" "1" AND   |

The functions observed in a case where the magnetization arrangement of the SEST1 (130) is the antiparallel arrangement (AP) and the magnetization arrangement of the SEST2 (140) is the parallel arrangement (P) are now described. Where the input  $V_A$  is "0" and the input  $V_B$  is "0", the output  $V_M$  of the output terminal 152 of the INV1 (190) is "1", and the output  $V_{out}$  of the output terminal 182 of the INV2 (194) is "0". Where the input  $V_A$  is "1" and the input  $V_B$  is "1", the output  $V_M$  is "0", and the output  $V_{out}$  is "1". Where the input  $V_A$  is "0" and the input  $V_B$  is "1", or the input  $V_A$  is "1" and the output  $V_M$  is "0", the output  $V_M$  is almost "0", and the output  $V_M$  is almost "1", since the input  $V_M$  is "0.5". In this manner, the logic circuit in accordance with the second embodiment functions as a two-input OR circuit.

Simulations of the output  $V_m$  of the INV1 (190) and the 45 output  $V_{out}$  of the INV2 (194) of the second embodiment were performed. FIG. 14 shows the capacitance values, the resistance values, and the voltage values used in the simulations. FIGS. 15 and 16 show the results of the simulations of the output  $V_m$  and the output  $V_{out}$ . FIG. 15 shows the results 50 obtained in a case where the magnetization arrangement of the SEST1 (130) is the parallel magnetization, and the magnetization arrangement of the SEST2 (140) is the antiparallel arrangement. FIG. 16 shows the results obtained in a case where the magnetization arrangement of the SEST1 (130) is 55 the antiparallel magnetization, and the magnetization arrangement of the SEST2 (140) is the parallel arrangement. The abscissa axis indicates the outputs  $\mathbf{V}_{m}$  and  $\mathbf{V}_{out}$  in a case where the input  $V_A$  and  $V_B$  are "0" or "1", with the low level being "0" and the high level being "1" in standardization. The 60 lower line of each of the outputs  $V_m$  and  $V_{out}$  represents "0", while the upper line of each of the outputs  $V_m$  and  $V_{out}$ represents "1".

In this manner, by varying the magnetization direction (the magnetization arrangement) of a ferromagnetic island having a variable magnetization direction (magnetization arrangement), a logic circuit that can reconfigure a two-input AND

18

circuit function and a two-input OR circuit function in a nonvolatile manner can be realized.

As can be seen from Table 2, FIG. 15, and FIG. 16, the output  $V_m$  of the INV1 (190) exhibits the function of a NOR circuit in a case where the magnetization arrangement of the SEST1 (130) is the antiparallel magnetization (AP), and the magnetization arrangement of the SEST2 (140) is the parallel arrangement (P), and exhibits the function of a NAND circuit in a case where the magnetization arrangement of the SEST1 (130) is the parallel magnetization (P), and the magnetization arrangement of the SEST1 (140) is the antiparallel arrangement (AP). In other words, a logic circuit that can reconfigure a Boolean logic circuit function can be achieved only with the INV1 of the second embodiment. However, to achieve outputs closer to "0" and "1", it is preferable that the INV2 (192) is provided as in the second embodiment.

As described above, in accordance with the second embodiment, by varying the magnetization direction of each ferromagnetic island having a variable magnetization direction, a two-input AND circuit function and a two-input OR circuit function can be reconfigured in a nonvolatile manner. Furthermore, as SESTs are used as transistors, the charge amount to be controlled is small. Accordingly, analog inputs can be made by combining the small gate capacitances between the islands and gates. With this structure, there is no need to use a floating gate that requires an area 100 or more times as large as the area of a transistor, as in the conventional technique 2. Accordingly, the circuit area can be made very small, compared with the circuit area obtained by the conventional technique 2. Further, the power consumption and the area of each SEST as a transistor are small. Thus, this embodiment can provide a logic circuit that can reconfigure an AND circuit function and an OR circuit function in a nonvolatile manner, and has a small circuit area and small power consumption.

## Third Embodiment

A third embodiment is an example of an asymmetrical logic circuit including SESTs. First, the principles of this embodiment are described. The broken line in FIG. 17 indicates the input/output curve of the inverter circuit of the first embodiment shown in FIG. 11 in a case where the magnetization arrangement of each of the SEST1 (100) and the SEST2 (110) is the parallel arrangement (P). In such a case, the inverter circuit becomes an inverter having a logic threshold value of 0.5.

In a case where an input is equal to or smaller than "0.5"  $(V_1)$ , the output is greater than "0.5". When an inverter circuit having an A-D converter function is connected in the next stage, almost "0" can be output. In a case where the input is equal to or greater than "0.5"  $(V_2)$ , the output is smaller than "0.5". When an inverter circuit having an A-D converter function is connected in the next stage, almost "1" can be output.

In a case where the magnetization arrangement of the SEST1 (100) is the parallel arrangement (P) while the magnetization arrangement of the SEST2 (110) is the antiparallel arrangement (AP) (the dotted line in FIG. 17), the output is larger than "0.5" whether the input is  $V_1$  or  $V_2$ , and almost "0" can be output by an inverter circuit having an A-D converter function in the next stage. On the other hand, in a case where the magnetization arrangement of the SEST1 (100) is the antiparallel arrangement (AP) while the magnetization arrangement of the SEST2 (110) is the parallel arrangement (P) (the solid line in FIG. 17), the output is smaller than "0.5"

whether the input is  $V_1$  or  $V_2$ , and almost "1" can be output by an inverter circuit having an A-D converter function in the next stage.

Accordingly, a logic circuit that can reconfigure the function of an AND/OR/asymmetric function "1010" can be realized, if "0",  $V_1$  (<"0.5"),  $V_2$  (>"0.5"), and "1" can be realized as analog inputs.

The gate capacitances 137a and 147a connected to the first input terminal 150 of the circuit structure of the second embodiment shown in FIG. 13 are replaced with  $xC_{in}$ , and the gate capacitances 137b and 147b connected to the second input terminal 151 are replaced with  $(1-x)C_{in}$ . Here, x is greater than 0 and is smaller than 0.5.

FIG. 18 is a circuit diagram of the logic circuit in accordance with the third embodiment. The circuit structure is the same as that of the second embodiment, except for the capacitance values. A first inverter circuit INV1 (432) includes a SEST1 (370) and a SEST2 (380). The source 372 of the SEST1 (370) is connected to an output terminal 392 of the INV1 (432), and the drain 374 is connected to a first power supply terminal 398. Tunnel junctions 373 and 375 are provided between an island 371 and the source 372 and between the island 371 and the drain 374, respectively. A first gate 376a is connected to a first input terminal 390, and a second gate 376b is connected to a second input terminal 391. A control gate 378 is grounded. A first gate capacitance 377a exists between the island 371 and the first gate 376a, and a second gate capacitance 377b exists between the island 371 and the second gate 376b. A control gate capacitance 379 exists between the island 371 and the control gate 378.

The source 382 of the SEST2 (380) is grounded (or connected to the second power supply terminal), and the drain 384 is connected to the output terminal 392 of the INV1 (432). Tunnel junctions 383 and 385 are provided between an island 381 and the source 382 and between the island 381 and the drain 384, respectively. A first gate 386a is connected to the first input terminal 390, and a second gate 386b is connected to the second input terminal 391. A control gate 388 is connected to a power supply  $V_{ad}$  396. A first gate capacitance 387a exists between the island 381 and the first gate 386a, and a second gate capacitance 387b exists between the island 381 and the second gate 386b. The output terminal 392 is grounded via a capacitance 394.

Further, the output terminal 392 of the INV1 (432) is connected to an input terminal 420 of the second inverter circuit (INV2) 430. The INV2 (430) is a Tucker-type inverter circuit, and includes a SET1 (400) and a SET2 (410) that are two single-electron transistors (SET).

The source 402 of the SET1 (400) is connected to an output terminal 422, and the drain 404 is connected to a power supply  $V_{dd}$  428. Tunnel junctions 403 and 405 are provided between an island 401 and the source 402 and between the island 401 and the drain 404, respectively. A gate 406 is connected to the output terminal 392 of the INV1 (432). A 55 control gate 408 is grounded. A gate capacitance 407 exists between the island 401 and the gate 406. A control gate capacitance 409 exists between the island 401 and the control gate 408.

The source 412 of the SET2 (410) is grounded, and the 60 drain 414 is connected to the output terminal 422. Tunnel junctions 413 and 415 are provided between an island 411 and the source 412 and between the island 411 and the drain 414, respectively. A gate 416 is connected to the output terminal 392 of the INV1 (432). A control gate 418 is connected to a 65 power supply  $V_{dd}$  426. A gate capacitance 417 exists between the island 411 and the gate 416. A control gate 419 is provided

20

between the island 411 and the control gate 418. The output terminal 422 is grounded via a capacitance 424.

As described above, the circuit structure of the third embodiment is the same as that of the second embodiment, except that the SEST1 (370) and the SEST2 (380) have difference gate capacitances.

Table 3 shows a truth table of inputs to the logic circuit in accordance with the third embodiment. Table 4 is a truth table of the logic circuit in accordance with the third embodiment. Simulations of the output  $V_{out}$  of the third embodiment were performed. FIG. 18 shows the capacitance values, the resistance values, and the voltage values that were used in the simulations. FIG. 19 shows the results of the  $V_{out}$  simulations. FIG. 19 shows the output  $V_{out}$  of the output terminal 422 of the INV2 (430) of each function (AND, OR, "0101") where the input  $V_A$  of the first input terminal 390 and the input  $V_B$  of the second input terminal 391 are "0" or "1". The low level is standardized as "0", and the high level is standardized as "1". The lower line of each of AND, OR, and "0101" indicates "0", and the upper line indicates "1".

TABLE 3

| $V_A$ | $V_B$ | Vin = XVA + (1 - X)VB |

|-------|-------|-----------------------|

| "0"   | "0"   | "()"                  |

| "0"   | "1"   | V2 = 1 - X > "0.5"    |

| "1"   | "0"   | V1 = X < "0.5"        |

| "1"   | "1"   | "1"                   |

TABLE 4

|              |              |                                                            | $V_{out}$ |        |     |        | _                                                             |

|--------------|--------------|------------------------------------------------------------|-----------|--------|-----|--------|---------------------------------------------------------------|

| SEST1        | SEST2        | $\begin{matrix} \mathbf{V}_A \\ \mathbf{V}_B \end{matrix}$ |           | 0<br>1 | 1   | 1<br>1 | $V_m$ (in order of Vm) function                               |

| AP<br>P<br>P | P<br>AP<br>P |                                                            | "1"       | "1"    | "1" | "0"    | "0" "1" "1" "1" OR "0" "0" "0" "1" AND "0" "1" "0" "1" "0101" |

In a case where the magnetization arrangement of the SEST1 (370) is the antiparallel arrangement (AP) and the magnetization arrangement of the SEST2 (380) is the parallel arrangement (P), the logic circuit in accordance with the third embodiment exhibits an OR circuit function. In a case where the magnetization arrangement of the SEST1 (370) is the parallel arrangement (P) and the magnetization arrangement of the SEST2 (380) is the antiparallel arrangement (AP), the logic circuit in accordance with the third embodiment exhibits an AND circuit function. In a case where the magnetization arrangement of each of the SEST1 (370) and the SEST2 (380) is the parallel arrangement (P), the logic circuit in accordance with the third embodiment exhibits a "0101" function.