US007545013B2

# (12) United States Patent

Sugahara et al.

## (10) **Patent No.:**

US 7,545,013 B2

## (45) **Date of Patent:**

Jun. 9, 2009

## (54) RECONFIGURABLE LOGIC CIRCUIT USING A TRANSISTOR HAVING SPIN-DEPENDENT TRANSFER CHARACTERISTICS

(75) Inventors: Satoshi Sugahara, Kanagawa (JP);

Tomohiro Matsuno, Tokyo (JP); Masaaki Tanaka, Saitama (JP)

(73) Assignee: Japan Science and Technology Agency,

Kawaguchi-shi (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 450 days.

(21) Appl. No.: 10/550,652

(22) PCT Filed: Mar. 26, 2004

(86) PCT No.: **PCT/JP2004/004379**

§ 371 (c)(1),

(2), (4) Date: **Dec. 7, 2005**

(87) PCT Pub. No.: WO2004/086625

PCT Pub. Date: Oct. 7, 2004

#### (65) Prior Publication Data

US 2006/0114018 A1 Jun. 1, 2006

## (30) Foreign Application Priority Data

(51) **Int. Cl.** *H01L 29/739* (2006.01)

See application file for complete search history.

### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,652,445 | Α            |   | 7/1997  | Johnson           |

|-----------|--------------|---|---------|-------------------|

| 5,654,566 | $\mathbf{A}$ | * | 8/1997  | Johnson 257/295   |

| 5,661,421 | $\mathbf{A}$ | * | 8/1997  | Ohmi et al 327/63 |

| 5,998,842 | Α            |   | 12/1999 | Sano              |

#### FOREIGN PATENT DOCUMENTS

| EP | 0 685 808 A1 | 12/1995 |

|----|--------------|---------|

| JP | A-05-343984  | 12/1983 |

| JP | A-61-234623  | 10/1986 |

| IΡ | A-06-250994  | 9/1994  |

#### (Continued)

## OTHER PUBLICATIONS

Notification of Reasons for Refusal, Mar. 25, 2008.

(Continued)

Primary Examiner—Eugene Lee (74) Attorney, Agent, or Firm—Oliff & Berridge, PLC

## (57) ABSTRACT

A nonvolatilely reconfigurable logical circuit is built. It is a reconfigurable logical circuit based on the CMOS configuration using the spin MOSFET. By changing the transmission characteristic of each transistor in accordance with the magnetization states of Tr1, Tr2, Tr5, and Tr8 which are spin MOSFETs, it is possible to reconfigure all the two-input symmetric functions AND/OR/XOR/NAND/NOR/XNOR/"1"/"0". Since it is possible to constitute the logical function by a small number of non-volatile elements, it is possible to reduce the chip area, thereby increasing the speed and reducing the power consumption.

### 40 Claims, 51 Drawing Sheets

SEMICONCUCTOR 11

## FOREIGN PATENT DOCUMENTS

| JP | A-09-097906   | 4/1997  |

|----|---------------|---------|

| JP | A-11-340542   | 12/1999 |

| JP | A-2000-349619 | 12/2000 |

| JP | A-2002-246487 | 8/2002  |

| JP | A-2003-008105 | 1/2003  |

| JP | A-2003-060211 | 2/2003  |

| JP | A-2003-092412 | 3/2003  |

#### OTHER PUBLICATIONS

S. Sugahara et al.; "A Spin MOSFET and its Applications"; The Magnetics Society of Japan; vol. 134; Jan. 2004; pp. 93-100. (w/abstract).

Stephen Trimberger; "A Reprogrammable Gate Array and Applications"; *Proceedings of the IEEE*; vol. 81, No. 7; Jul. 1993; pp. 1030-1041.

Scott Hauck; "The Roles of FPGA's in Reprogrammable Systems"; *Proceedings of the IEEE*; vol. 86, No. 4; Apr. 1998; pp. 615-638. Toshinori Sueyoshi; "Programmable Logic Devices—from the Past to the Future"; *Technical Report of IEICE*; vol. 101, No. 632; 2002; pp. 17-24 (w/ abstract).

Tadashi Shibata et al.; "A Functional MOS Transistor Featuring Gate-Level Weighted Sum and Threshold Operations"; *IEEE Transactions on Electron Devices*; vol. 39, No. 6; Jun. 1992; pp. 1444-1455.

Tadashi Shibata et al.; Neuron MOS Binary-Logic Integrated Circuits-Part I: Design Fundamentals and Soft-Hardware-Logic Circuit Implementation; *IEEE Transactions on Electron Devices*; vol. 40, No. 3, Mar. 1993; pp. 570-576.

Hiroshi Sawada et al; "Consideration for a Reconfigurable Logic Device using Neuron MOS Transistors"; Technical Report of IEICE; vol. 99, No. 481; Nov. 1999; pp. 41-48. (w/ abstract).

<sup>\*</sup> cited by examiner

FIG. 1A

FIG. 1B

FIG. 2A

FIG. 2B

FIG. 3A FIG. 3B

FIG. 4

FIG. 5A

FIG. 5B

Jun. 9, 2009

FIG. 5C

FIG. 6

FIG. 7

FIG. 8

FIG. 9

| (A) |     |        |      |   | (E      | 3)   |      |

|-----|-----|--------|------|---|---------|------|------|

|     | βn1 | = 1    |      |   | βn i    | = 10 |      |

| Α   | В   | Vm     | Vout | Α | В       | Vm   | Vout |

| 0   | 0   | VO     | "0"  | 0 | 0       | VO   | "0"  |

| 0   | 1   | VP     | "1"  | 0 | 1       | VR   | "0"  |

| 1   | 1   | VQ     | "1"  | 1 | 1       | VS   | "1"  |

|     | 0   | ı<br>R | l    | , | ı<br>Al | ND   | 1 1  |

FIG. 10

FIG. 11

FIG. 12C

$\beta n1 = 1$  $\beta n1 = 10$ Id of Tr1, (Tr2 - Tr5) A = B = "1" Vm Vout Vout Vm VO 0 0 VO 0 A or B = "I" 0 A = B = "0" VP 0 VR 0 0 vs /  $\beta$ n1 = 10 1 ٧Q 1 VS  $\beta n 1 = 1$ VR vo OR AND ٧m

$\beta$ m5 = 0.5,  $\beta$ n1 = 1 or 10

FIG. 12 B

FIG. 12A

Vin

FIG. 13A

|   | Α    | В | Vm | Vout |  |  |

|---|------|---|----|------|--|--|

| • | 0    | 0 | VT | 0    |  |  |

|   | 0    | 1 | VR | 0    |  |  |

|   | 1    | 1 | ΥŞ | ì    |  |  |

|   | ,    |   |    | J    |  |  |

|   | XNOR |   |    |      |  |  |

$\beta n5 = 50$ ,  $\beta n1 = 10$

FIG.14A

FIG. 14B

$\beta n5 = 50, \beta n1 = 1$

FIG. 16A

FIG. 17

FIG. 18

FIG. 19A

FIG. 19B

| Α | В | Vm | Vout |

|---|---|----|------|

| 0 | 0 | VO | "0"  |

| 0 | 1 | VP | "1"  |

| 1 | 1 | VQ | "1"  |

|   | l |    |      |

|   |   | OR |      |

$\beta p1 = 1$ ,  $\beta n2 = 10$

FIG. 20A FIG. 20B

$\beta p1 = 10, \beta n2 = 1$

FIG. 21

FIG. 22A

| A | В | Vm | Vout |

|---|---|----|------|

| 0 | 0 | VO | '"0" |

| 0 | 1 | VP | "1"  |

| 1 | 1 | VQ | "["  |

|   |   |    |      |

|   |   | OR |      |

| A | 0 | 0 | 1 |

|---|---|---|---|

| В | 0 | 1 | 1 |

$$Vinv1_low (\beta p1 = 1, \beta n2 = 10)$$

FIG. 23A

FIG. 23B

| A   | В | Vm | Vout |  |  |

|-----|---|----|------|--|--|

| 0   | 0 | VO | "0"  |  |  |

| 0   | 1 | VR | "0"  |  |  |

| 1   | 1 | VQ | "1"  |  |  |

|     | ] |    | l    |  |  |

| AND |   |    |      |  |  |

| A | 0 | 0 | 1 |

|---|---|---|---|

| В | 0 | 1 | 1 |

$Vinv1_low (\beta p1 = 10, \beta n2 = 1)$

FIG. 24

Vinv3<Vdd/2

FIG. 25

FIG. 26B

Id of Tr1, (Tr2 + Tr5)

| Α  | В | Vm | Vout |  |  |  |

|----|---|----|------|--|--|--|

| 0  | 0 | VO | "0"  |  |  |  |

| 0  | 1 | VP | "1"  |  |  |  |

| 1  | 1 | VQ | "1"  |  |  |  |

|    |   |    |      |  |  |  |

| OR |   |    |      |  |  |  |

$$\beta p1 = 1$$

,  $\beta n2 = 10$ ,  $\beta n5 = 0.5$

FIG. 27A

FIG. 27B

Id of Tr1, (Tr2 + Tr5)

| A   | В | Vm | Vout |  |  |

|-----|---|----|------|--|--|

| 0   | 0 | VO | "0"  |  |  |

| 0   | 1 | VR | "0"  |  |  |

| 1   | 1 | VQ | "1"  |  |  |

| AND |   |    |      |  |  |

$\beta p1 = 10$ ,  $\beta n2 = 1$ ,  $\beta n5 = 0.5$

FIG. 28A FIG. 28B

Id of Tr1, (Tr2 + Tr5)

| A   | В       | Vm | Vout |  |

|-----|---------|----|------|--|

| 0   | 0       | VT | "1"  |  |

| 0   | 1       | VP | "1"  |  |

| 1   | 1       | VQ | "1"  |  |

| l i |         |    |      |  |

|     | all "1" |    |      |  |

$\beta p1 = 1, \beta n2 = 10, \beta n5 = 50$

FIG. 29A FIG. 29B

Id of Tr1, (Tr2 + Tr5)

| Α     | В | Vm | Vout |  |

|-------|---|----|------|--|

| 0     | 0 | VS | "1"  |  |

| 0     | I | VR | "0"  |  |

| 1     | 1 | VQ | "1"  |  |

| 1 1 1 |   |    |      |  |

| XNOR  |   |    |      |  |

$$\beta p1 = 10, \beta n2 = 1, \beta n5 = 50$$

FIG. 30

FIG. 31

FIG. 32 A

FIG. 32B

| A   | В | Vm | Vout         |  |

|-----|---|----|--------------|--|

| 0   | 0 | VO | "0"          |  |

| 0   | 1 | VP | "1"          |  |

| 1   | 1 | VT | " <u>0</u> " |  |

| 1 1 |   |    |              |  |

| XOR |   |    |              |  |

$$\beta p1 = 1$$

,  $\beta n2 = 10$ ,  $\beta n5 = 0.5$ ,  $\beta p8 = 50$

FIG. 33A

FIG. 33B

$$Id of (Tr1 + Tr8), (Tr2 + Tr5)$$

| Α       | В | Vm | Vout |  |

|---------|---|----|------|--|

| 0       | 0 | VO | "0"  |  |

| 0       | 1 | VR | "0"  |  |

| 1       | 1 | VU | "0"  |  |

| 1 1 1   |   |    |      |  |

| all "0" |   |    |      |  |

$\beta p1 = 10, \beta n2 = 1, \beta n5 = 0.5, \beta p8 = 50$

FIG. 34A

FIG. 34B

Id of (Tr1 + Tr8), (Tr2 + Tr5)

| Α    | В | Vm | Vout |  |  |

|------|---|----|------|--|--|

| 0    | 0 | VT | "1"  |  |  |

| 0    | 1 | VP | "1"  |  |  |

| 1    | 1 | VU | "0"  |  |  |

| 1 1  |   |    |      |  |  |

| NAND |   |    |      |  |  |

$\beta p1 = 1$ ,  $\beta n2 = 10$ ,  $\beta n5 = 50$ ,  $\beta p8 = 50$

FIG. 35A FIG. 35B

Id of (Tr1 + Tr8), (Tr2 + Tr5)

| Α     | В | Vm | Vout |  |

|-------|---|----|------|--|

| 0     | 0 | VS | "1"  |  |

| 0     | 1 | VR | "0"  |  |

| 1     | 1 | VV | "0"  |  |

| 1 1 1 |   |    |      |  |

| NOR   |   |    |      |  |

$\beta$ p1 = 10,  $\beta$ n2 = 1,  $\beta$ n5 = 50,  $\beta$ p8 = 50

FIG. 37

FIG. 38

FIG. 39

Vout

A

B

Vm

Vinv\_low

Vinv\_high

0

0

VO

1

1

0

1

VP

0

1

1

1

VQ

0

0

NOR

NAND

FIG. 40

FIG. 41

FIG. 42A

FIG. 42B

Id of Tr1, (Tr2 + Tr5)

|   |   |    |          | Vout      |

|---|---|----|----------|-----------|

| Α | В | Vm | Vinv_low | Vinv_high |

| 0 | 0 | VO | I        | 1         |

| 0 | 1 | VP | 0        | 1         |

| 1 | 1 | VQ | 0        | 0         |

|   | 1 |    | NOR      | NAND      |

$\beta$ n5 = 1

FIG. 43A FIG. 43B

FIG. 44

FIG. 45

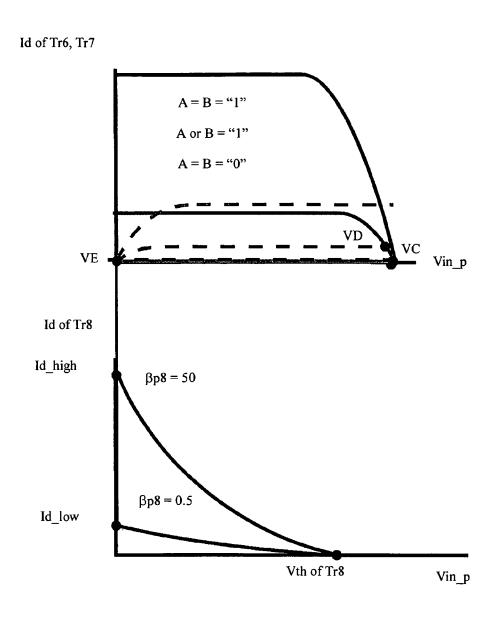

Id of Tr6, Tr7

FIG. 46A FIG. 46B

Id of (Tr1 + Tr8), Tr2

$\beta$ n5 = 1,  $\beta$ p8 = 10

FIG. 47A FIG. 47B

|   |   |    |          | out       |

|---|---|----|----------|-----------|

| Α | В | Vm | Vinv_low | Vinv_high |

| 0 | 0 | vo | 1        | 1         |

| 0 | 1 | VP | 0        | 1         |

| 1 | 1 | VQ | 0        | 0         |

|   |   |    | AND      | OR        |

FIG. 49

Jun. 9, 2009

NOR

FIG. 50

$\beta n2 = 10$

$\beta$ n2 = 1

FIG. 51A

Jun. 9, 2009

FIG. 51B

FIG. 52A

FIG. 52B

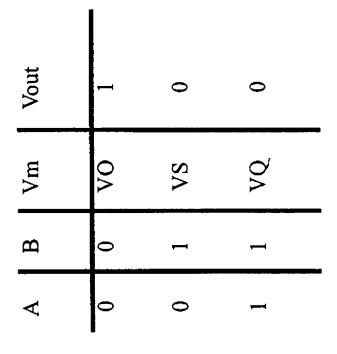

|   | βn | 2 = 1          |      |   | βn | 2 = 10         | ) |

|---|----|----------------|------|---|----|----------------|---|

|   |    |                | Vout |   |    | Vm             |   |

| 0 | 0  | VO             | 1    | 0 | 0  | VO             | 1 |

| 0 | 1  | VS             | 0    | 0 | 1  | VR             | 1 |

| 1 | 1  | vo<br>vs<br>vQ | 0    | 1 | 1  | VO<br>VR<br>VP | 0 |

| ' |    | NOR            |      | ' | N. | AND            |   |

$\beta m5 = 1$ ,  $\beta n2 = 1$  or 10

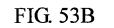

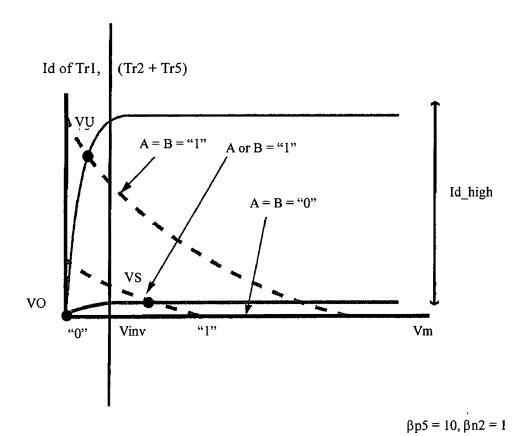

FIG. 53A

| Α    | В | Vm | Vout |  |  |  |  |  |  |  |

|------|---|----|------|--|--|--|--|--|--|--|

| 0    | 0 | VO | 1    |  |  |  |  |  |  |  |

| 0    | 1 | VS | 0    |  |  |  |  |  |  |  |

| 1    | 1 | VU | 1    |  |  |  |  |  |  |  |

| XNOR |   |    |      |  |  |  |  |  |  |  |

FIG. 54A

FIG. 54B

| Ä | В | Vm | Vout |

|---|---|----|------|

| 0 | 0 | VO | 1    |

| 0 | 1 | VR | 1    |

| 1 | 1 | VV | 1    |

all "1"

FIG. 55

FIG. 56

# RECONFIGURABLE LOGIC CIRCUIT USING A TRANSISTOR HAVING SPIN-DEPENDENT TRANSFER CHARACTERISTICS

## FIELD OF THE INVENTION

The present invention relates to logic circuits with reconfigurable functions, and more particularly, to a reconfigurable logic circuit using transistors (hereafter referred to as the "spin transistors") that contain ferromagnetic bodies and 10 have transfer characteristics depending on the magnetization states of the ferromagnetic bodies.

#### BACKGROUND OF THE INVENTION

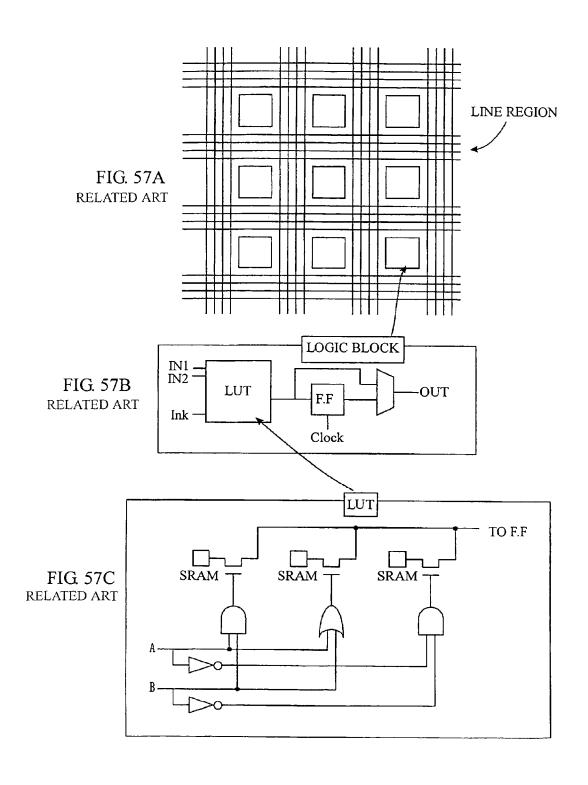

Recently, attention has been drawn to logic circuits that can reconfigure (or reprogram) functions in accordance with user programs. For example, a field programmable logic array (FPGA) that has been developed by the LSI technique is widely used (disclosed by S. Trimberger in Proc. IEEE 81 20 (1993) pp. 1030-1041, S. Hauck in Proc. IEEE 86 (1998) pp. 615-638, and Toshinori Sueyoshi in "Programmable Logic Devices" IEICE Tech. Report, Vol. 101, No. 632, (2002) pp. 17-24, for example). Conventionally, the FPGA has been used only for test products and limited products. However, 25 since shipment can be made quickly and the functions can be rewritten after shipment, the FPGA is incorporated as the last component into mobile devices such as portable telephone devices that tend to be replaced with newly developed devices in a short time. Also, studies have been made on the FPGA as 30 an information device of novel architecture that reconfigures its hardware for each operation.

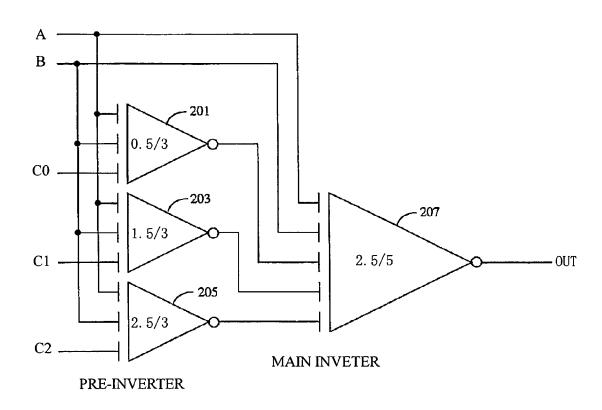

There are several types of configurations for the FPGA. Among them, the Look Up Table (LUT) method using SRAMs is most widely used. In this configuration, small-sized logic blocks that are formed with LUTs for achieving desired functions are arranged in a matrix fashion, and the blocks are connected to one another with lines that can be changed by a switch (a pass transistor, for example) (see FIG. 57A)

A desired logic circuit is realized by rewriting the values to be written in the register of the LUT and the switch for the lines. Each logic block includes a flip-flop (FF) for operations in synchronization with the LUT (see FIG. 57B). The LUT includes a decoder circuit for matching each input pattern 45 with an address, and memories (SRAM cells) for storing a value in the register of each address. FIG. 57C shows an example of the LUT circuit that can achieve symmetric Boolean functions.

A SRAM is a volatile memory, and loses stored information when the power supply is cut off. Therefore, so as to maintain data, a non-volatile memory (a flash memory, for example) is prepared externally, and the information stored in the non-volatile memory is loaded every time the power supply is resumed.

Recently, studies have been made on a circuit that has a neuron MOS (hereinafter referred to as the "vMOS") in the logic circuit blocks. This circuit has been developed as a reconfigurable logic circuit based on principles entirely different from those of the FPGA according to the LUT method (disclosed by T. Shibata and T. Ohmi in IEEE Trans. Electron Dev. ED-39 (1992) pp. 1444-1455 and IEEE Trans. Electron Dev. ED-40 (1993) pp. 570-576, and by Hiroshi Sawada, Kazuo Aoyama, Akira Nagoya, and Kazuo Nakajima in "Consideration for a Reconfigurable Logic Device using 65 Neuron MOS Transistors", IEICE Tech. Report, Vol. 99, No. 481, (1999) pp. 41-48). Using vMOS, symmetric functions

2

can be efficiently realized. Although the functions are limited compared with the functions according to the LUT method, attention is being drawn to this method, as a large number of symmetric functions appear in the stage of logic design.

FIG. **56** illustrates an example structure of a logic circuit that can achieve symmetric Boolean functions. This logic circuit includes three pre-inverters **201**, **203**, and **205** that employ νMOS structures, and a main inverter **207** that also employs the νMOS structure. In the pre-inverters that serve as input units, digital values are input via equal capacitances. The inverters **201**, **203**, **205**, and **207** have different logic threshold values from one another. In the drawing, V<sub>k</sub>/n indicates that the number of inputs to the inverter is n, and the logic threshold value is V<sub>k</sub>/n with respect to the logic level "1".

Also, inputs are denoted by A and B, and the input of each control signal is denoted by  $C_k$  (k=0, 1, 2). The input to the main inverter **207** is controlled with  $C_k$ , thereby achieving a desired symmetric function. In the operation of this circuit, if  $C_k$  is "1", the output is "0" only when the number of "1"s in the input is k. In other cases, the output is "1". For example, if  $C_0$  and  $C_2$  are "1" and  $C_1$  is "0", the output is "0" when the number of "1"s is O(A=B=0)0" and when the number of "1"s is O(A=B=0)1", but the output is "1" when the number of "1"s is O(A=B=0)1". Thus, a XOR logic circuit is obtained.

## DISCLOSURE OF THE INVENTION

The above described logic blocks of the FPGA have the following problems. More specifically, the logic blocks that utilizes the LUT method and vMOS have problems in the volatility of logic functions. Also, problems are caused with respect to the number of devices (the occupied area).

First, the problems with the logic blocks according to the LUT method, the circuit does not have capacity to rewrite to reconfigure logics, but refers to the values stored in the registers. SRAMs are employed for LUTs, the problems are caused by the volatility of the SRAMs. When the power supply is cut off, the contents of the LUTs, or the logic functions, are lost. In a case where the circuit is incorporated into a product, it is necessary to externally provide a non-volatile memory with an extremely large capacity for maintaining data. As a result, the area of the entire chip becomes larger, and the power consumption increases as a longer start-up time is required when power supply is resumed.

Also, in a case where a large number of devices (forty transistors are required in the circuit of FIG. **56**C, for example) are employed to achieve symmetric Boolean functions with decoders and SRAM cells including transistors in the logic blocks, the area occupied by the logic blocks becomes larger.

Next, the problems with the logic blocks using vMOS are described. In such logic blocks, the operation of the circuit can be rewritten with a control signal, unlike in the logic blocks according to the LUT method. For two inputs, the number of MOSFETs is 8, and the number of capacitors is 14, which are almost half of the number of devices required according to the LUT method. However, the area occupied by the capacitors for the vMOS structure is not small. Also, to maintain the functions of the circuit, a control signals needs to be constantly supplied during the use of the circuit. It is also necessary to prepare a control signal of a size different from the supply voltage and to employ a control circuit (a controller) for controlling the control signal. Since functions cannot

be stored in a non-volatile manner, there is a problem in the maintenance of the non-volatility for logic functions, as with the LUT method.

It is therefore an object of the present invention to provide a non-volatilely reconfigurable circuit with a small number of 5 devices. Such a circuit should be small in size and have low power consumption.

In a circuit in accordance with the present invention, a transistor (hereinafter referred to as "spin transistor") with transfer characteristics that depend on the spin direction of the conduction carriers or the magnetization states of the ferromagnetic bodies in the transistor is employed, and the input of the transistor is formed with a vMOS transistor. The operating point of the circuit is adjusted to rewrite functions by varying the driving force of the transistor through the 15 control of the magnetization state of the spin transistor. This circuit is based on a novel technique of rewriting functions entirely in terns of hardware, as the characteristics of the device are changed. This circuit differs from a logic block only with a vMOS in that logic functions can be maintained in 20 a non-volatile manner and a control signal is not required for switching logic functions. Furthermore, the functions of the circuit can be stored in a non-volatile manner, by virtue of the ferromagnetic bodies in the spin transistor. Using such a logic circuit of the present invention, the above described problems 25 in FPGA can be eliminated.

The non-volatility is now described. The functions of a circuit are determined by the magnetization states of the ferromagnetic bodies included in the spin transistor. Accordingly, even when the power supply is cut off, the logic functions are maintained in a non-volatile manner, as the magnetization states do not change. In view of this, the portion corresponding to a logic block unit that is necessary in the conventional FPGA becomes unnecessary in an external non-volatile memory. This is advantageous in reducing the chip 35 size. Furthermore, the time for loading logic functions is not required. Accordingly, the time required for start-up can also be shortened.

In a circuit in accordance with the present invention, the logic block includes nine to eleven MOSFETs and two 40 capacitors. Accordingly, the number of devices decreases to a third of the number of device in the LUT structure or even less than that. Compared with a logic block using only a vMOS, the number of devices is halved. Since the external non-volatile memories are employed only for the line unit, the 45 total number of devices is much smaller than that in a conventional circuit.

A spin transistor can be employed as a switch for selecting the line that connects logic blocks. Especially, a spin MOS-FET that is described later is employed as the switch, so that the mutual lines between logic blocks can also be stored in a non-volatile manner. In such a case, a non-volatile memory becomes unnecessary for the line unit. The spin MOSFET as the switch may be a depletion MOSFET or an enhancement MOSFET. Further, a transfer gate that is formed with p-channel and n-channel spin MOSFETs can also be employed.

One aspect of the present invention can provide a circuit that includes a spin transistor having transfer characteristics depending on the spin direction of conduction carriers. In this circuit, the spin direction of the conduction carriers is 60 changed so as to vary the transfer characteristics of the spin transistor, and an operating point is changed based on the transfer characteristics, thereby reconfiguring a function.

An A-D converter is connected to an output terminal of the circuit, so that the analog operating point at the output terminal is converted to a digital logic level. Also, the A-D converter includes a spin transistor, so that functions can be

4

reconfigured by setting a threshold value depending on the magnetization state of the spin transistor.

Instead of the spin transistor, another spin transistor with variable transfer characteristics can be employed in the circuit. In such a case, the operating point is also moved by changing the transfer characteristics of the transistor, thereby reconfiguring functions. Here, the "variable transfer characteristics" are variable solid-state properties other than the biases such as  $V_{ds}$  and  $V_{gs}$ , and the transfer characteristics of a transistor can be varied in a non-volatile manner. Accordingly, the output characteristics vary, even when biases are applied under the same conditions. Such a transistor can be realized with a ferromagnetic material or a ferroelectric material, or can be formed by a floating gate technique (by which carriers are injected to a floating gate so as to change a threshold value). The above described spin transistor is one of the transistors with variable transfer characteristics.

## BRIEF DESCRIPTION OF THE DRAWINGS

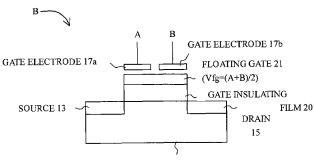

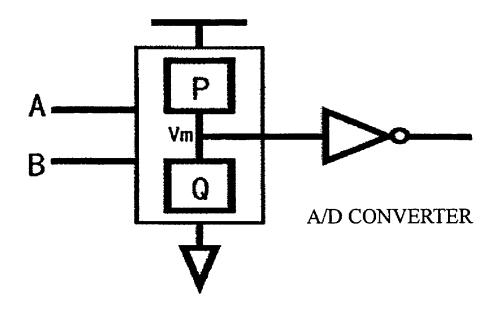

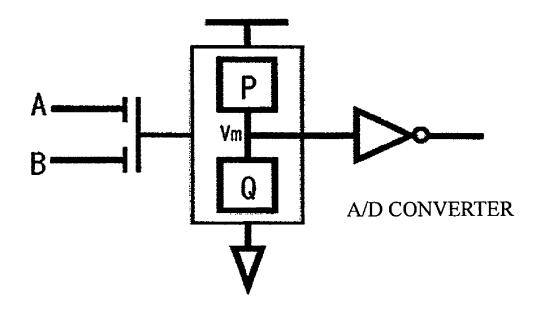

FIGS. 1A and 1B are block diagrams each illustrating the fundamental structure of a circuit in accordance with the present invention;

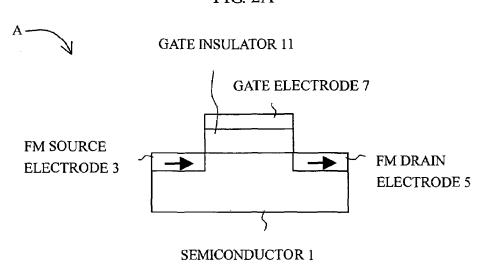

FIG. **2**A illustrates an example structure of a MOSFET-type spin transistor (hereinafter referred to as "spin MOSFET");

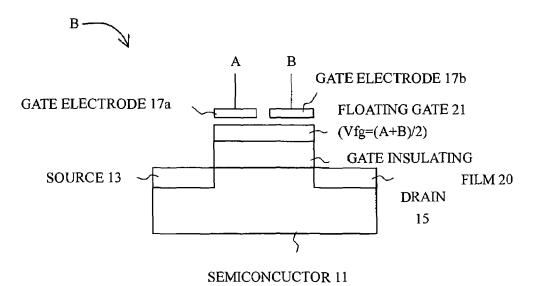

FIG. 2B illustrates an example structure of a vMOS (B);

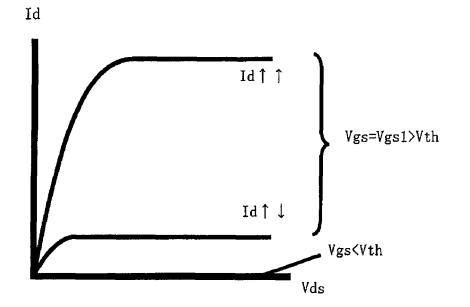

FIG. 3A shows the idealized static characteristics of a spin MOSFET;

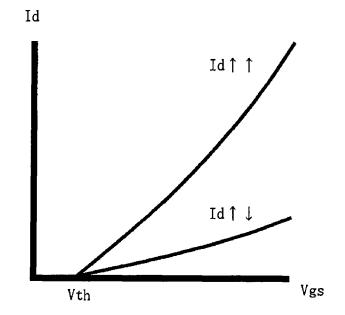

FIG. 3B shows the gate voltage dependence of the drain current;

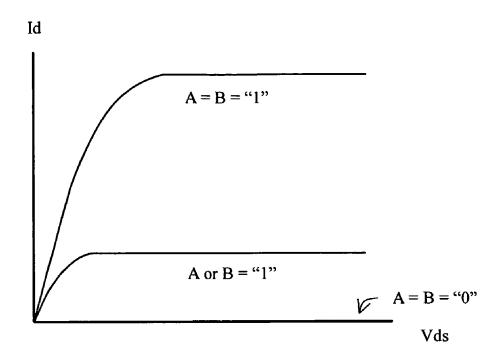

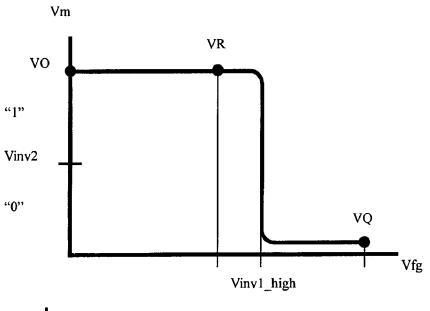

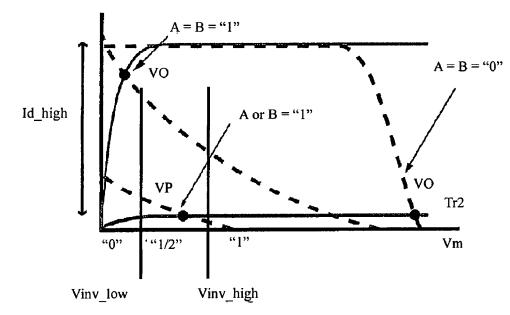

FIG. 4 shows the static characteristics of the vMOS transistor of FIG. 2B, with the inputs A and B being digital values;

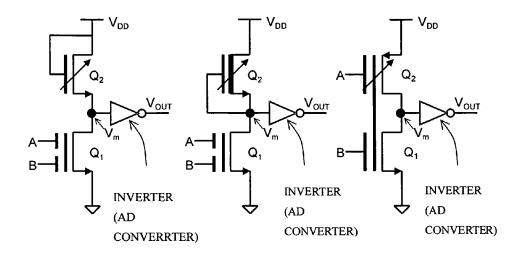

FIGS. 5A, 5B, and 5C show AND/OR reconfigurable logic circuits with E/E, E/D, and CMOS inverter structures;

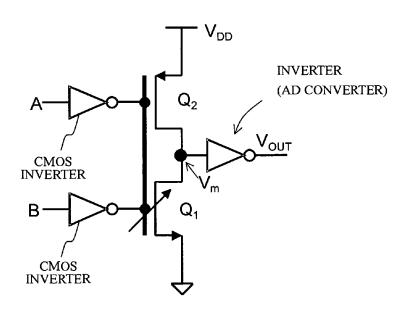

FIG. 6 illustrates an example structure of a NAND/NOR reconfigurable logic circuit, with a CMOS inverter for an input;

FIG. 7 illustrates an AND/OR circuit with a n-channel spin MOSFET of a depletion type;

FIG. **8** shows the operating curve of an AND/OR circuit with the n-channel spin MOSFET of a depletion type;

$FIGS.\ 9A$  and 9B are truth tables of the AND/OR circuit with the n-channel spin MOSFET of a depletion type;

FIG. 10 illustrates a circuit that has a XNOR function added to the circuit illustrated in FIG. 7;

FIG. 11 illustrates a first operation of the circuit illustrated in FIG. 10;

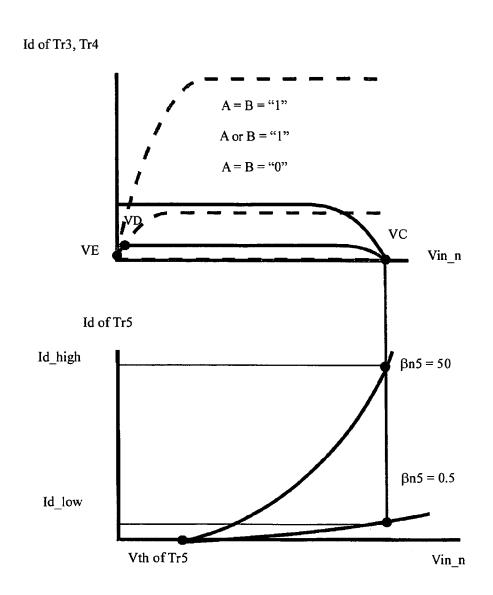

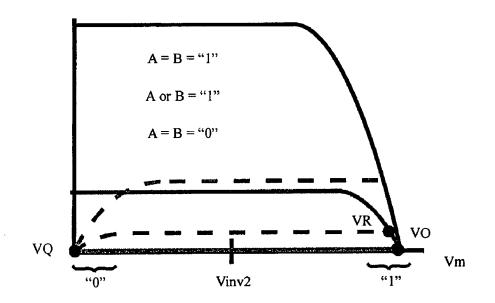

FIG. 12A shows the operating curve of the AND/OR function:

FIG. 12B shows a truth table of the OR circuit;

FIG. 12C shows a truth table of the AND circuit;

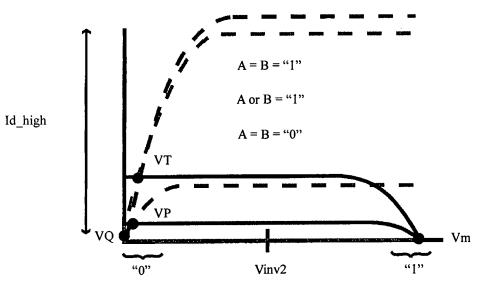

FIG. 13A shows the operating curve of the XNOR function;

FIG. 13B shows a truth table of the XNOR circuit;

FIG. 14A illustrates a third operation of the circuit illustrated in FIG. 10;

FIG. 14B is a truth table of the operation;

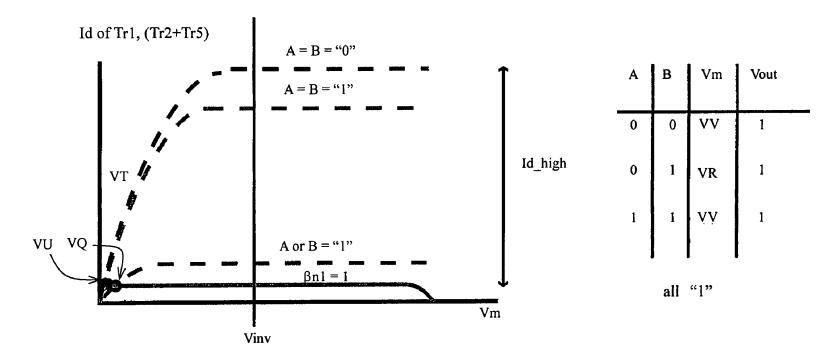

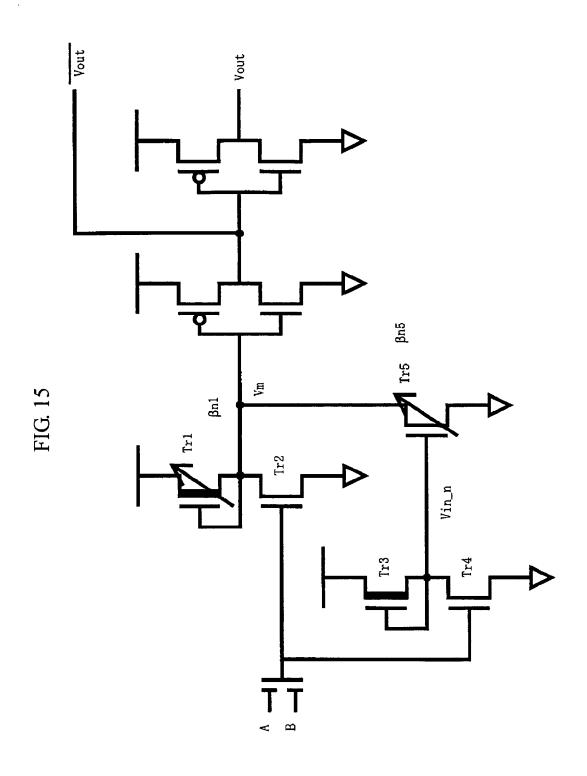

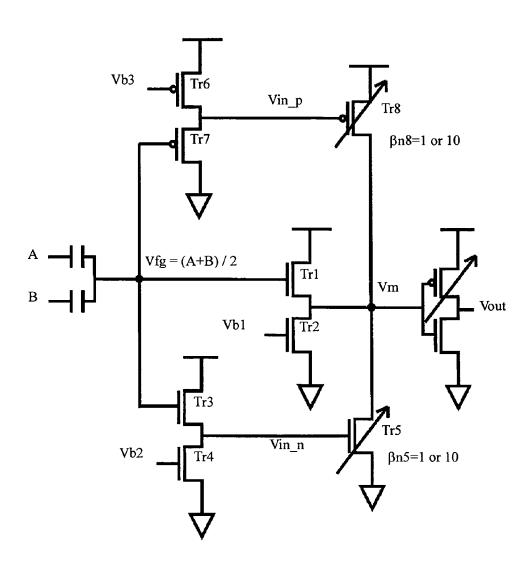

FIG. **15** illustrates the structure of a circuit that can reconfigure all the symmetric Boolean functions;

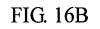

FIG. **16**A illustrates the circuit structure of a threshold value variable inverter;

FIG. 16B illustrates an example operation of the inverter;

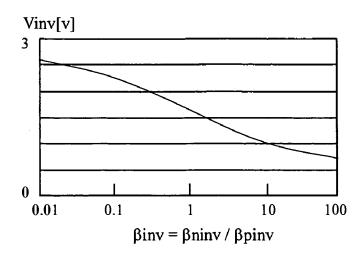

FIG. 17 has the threshold value of a conventional CMOS inverter as the function of the ratio of  $\beta$  of a pMOS to  $\beta$  of an nMOS;

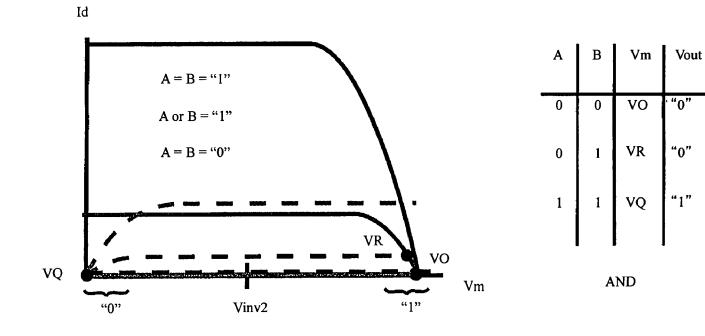

- FIG. 18 illustrates an example structure of an AND/OR circuit:

- FIG. **19**A shows a first operation of the circuit illustrated in FIG. **18**:

- FIG. 19B shows a truth table of the operation;

- FIG. 20A shows a second operation of the circuit illustrated in FIG. 18;

- FIG. 20B shows a truth table of the operation;

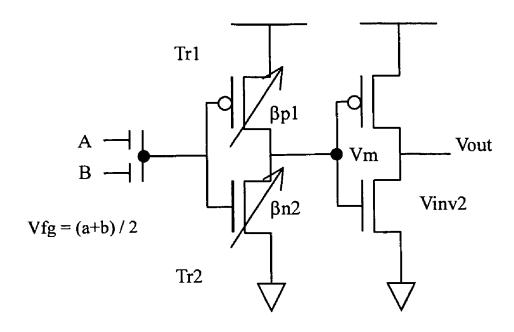

- FIG. 21 shows another example structure of an AND/OR circuit;

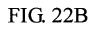

- FIG. 22A shows the characteristics of the variable threshold value inverter of FIG. 21;

- FIG. 22B shows a truth table of the inverter;

- FIG. 23A corresponds to FIG. 22A, showing the operation when the threshold value is varied;

- FIG. 23B corresponds to FIG. 22B, showing truth table;

- FIG. **24** illustrates an example structure of an AND/OR/XNOR circuit;

- FIG. **25** shows the operating curve of Vin\_n of the circuit illustrated in FIG. **24**:

- FIG. 26A shows a first operation of the circuit illustrated in FIG. 24;

- FIG. 26B shows a truth table of the operation;

- FIG. 27A shows a second operation of the circuit illustrated in FIG. 24;

- FIG. 27B shows a truth table of the operation;

- FIG. 28A shows a third operation of the circuit illustrated in FIG. 24;

- FIG. 28B shows a truth table of the operation;

- FIG. 29A shows a fourth operation of the circuit illustrated 30 in FIG. 51A; in FIG. 24; FIG. 54B s

- FIG. 29B shows a truth table of the operation;

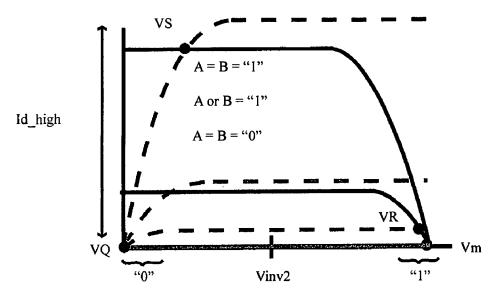

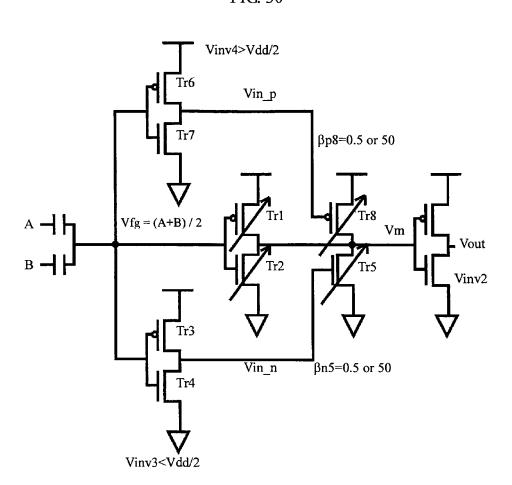

- FIG. 30 illustrates an example structure of an AND/OR/XOR/XNOR circuit;

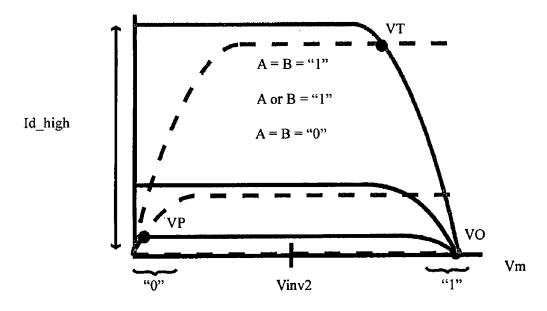

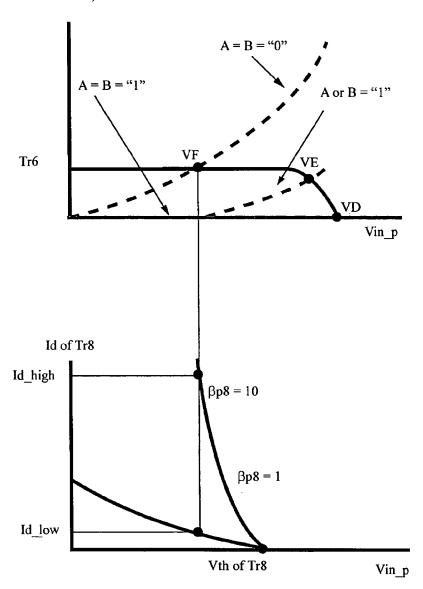

- FIG. 31 shows the operating points of Vin\_p of the circuit <sup>35</sup> illustrated in FIG. 30;

- FIG. **32**A shows a first operation of the circuit illustrated in FIG. **30**;

- FIG. 32B shows a truth table of the operation;

- FIG. 33A shows a second operation of the circuit illustrated in FIG. 30;

- FIG. 33B shows a truth table of the operation;

- FIG. **34**A shows a third operation of the circuit illustrated in FIG. **30**:

- FIG. **34**B shows a truth table of the operation:

- FIG. 35A shows a fourth operation of the circuit illustrated in FIG. 30:

- FIG. 35B shows a truth table of the operation;

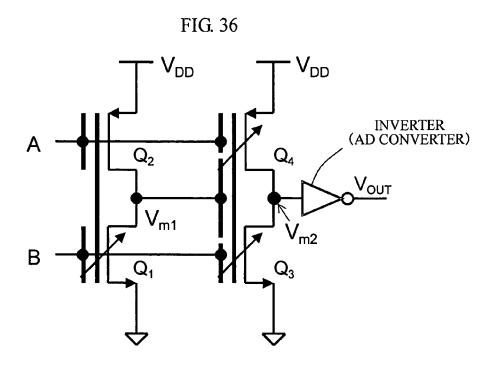

- FIG. **36** illustrates an example structure of a reconfigurable logic circuit with a spin MOSFET;

- FIG. 37 illustrates an example structure of a NAND/NOR circuit:

- FIG. 38 shows the operating points of the circuit illustrated in FIG. 37, and the characteristics of the inverter;

- FIG. 39 shows a truth table of the circuit illustrated in FIG. 37;

- FIG. 40 is a circuit diagram of a NAND/NOR/XNOR circuit;

- FIG. 41 shows the operating points of  $Vin_n$  of the circuit  $_{60}$  illustrated in FIG. 40:

- FIG. **42**A shows a first operation of the circuit illustrated in FIG. **40**;

- FIG. 42B shows a truth table of the operation;

- FIG. 43A shows a second operation of the circuit illus- 65 trated in FIG. 40;

- FIG. 43B shows a truth table of the operation;

6

- FIG. 44 is a circuit diagram of a NAND/NOR/XNOR/XOR circuit:

- FIG. 45 shows the operating points of Vin\_p of the circuit illustrated in FIG. 44;

- FIG. **46**A shows a first operation of the circuit illustrated in FIG. **44**;

- FIG. 46B shows a truth table of the operation;

- FIG. 47A shows a second operation of the circuit illustrated in FIG. 44;

- FIG. 47B shows a truth table of the operation;

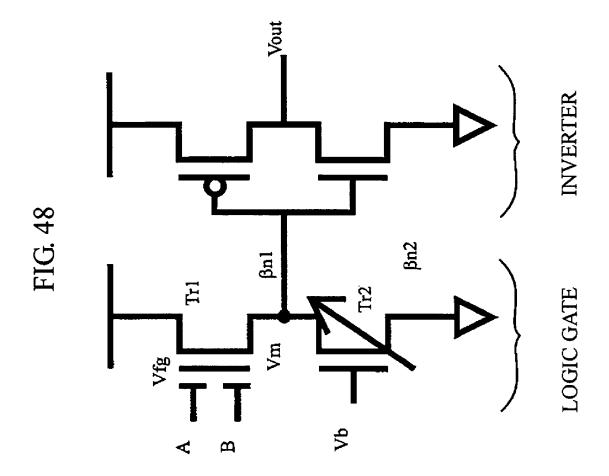

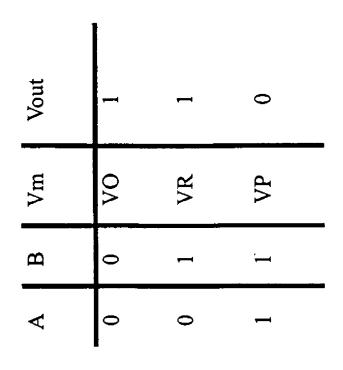

- FIG. **48** illustrates an example structure of a NAND/NOR circuit (E/E configuration);

- FIG. **49** illustrates the operation of the circuit illustrated in FIG. **48**:

- FIG. 50 shows truth tables of the NOR circuit and the NAND circuit shown in FIG. 48;

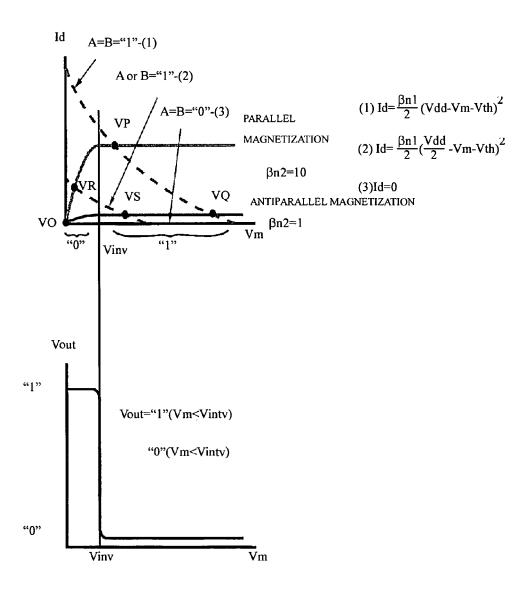

- FIG. **51**A illustrates an example structure of an NAND/NOR/XNOR circuit;

- FIG. **51**B shows the operating points of Vin\_n of the circuit 20 illustrated in FIG. **51**A:

- FIG. **52**A shows a first operation of the circuit illustrated in FIG. **51**A;

- FIG. 52B shows a truth table of the operation shown in FIG. 52A;

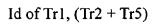

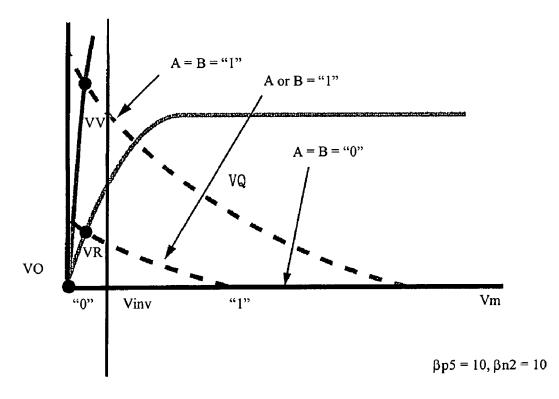

- 25 FIG. 53A shows a second operation of the circuit illustrated in FIG. 51A;

- FIG. **53**B shows a truth table of the operation shown in FIG. **53**A:

- FIG. **54**A shows a third operation of the circuit illustrated in FIG. **51**A.

- $FIG.\, {\bf 54}B \ shows \ a \ truth \ table \ of the \ operation \ shown \ in \ FIG. \ {\bf 54}A;$

- FIG. **55** illustrates the structure of a circuit that can reconfigure all the symmetric Boolean functions;

- FIG. **56** illustrates an example structure of a logic circuit with which symmetric Boolean functions can be realized;

- FIG. **57**A shows a circuit in which small-sized logic blocks having LUTs and memory devices that can achieve desired functions are arranged in a matrix fashion, and the blocks are connected with lines that can be changed by a switch (a pass transistor, for example);

- FIG. **57**B shows a circuit that includes a flip-flop (FF) for operating in synchronization with a LUT; and

- FIG. **57**C shows an example of a LUT circuit with which symmetric Boolean functions can be realized.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

Referring to FIGS. 1A and 1B, the fundamental structure of a circuit in accordance with the present invention is described. As shown in FIGS. 1A and 1B, the circuit in accordance with the present invention includes a terminal  $V_m$  (hereinafter, " $V_m$ " will be used as the name of the terminal, but will also be used as the potential of the terminal), a circuit group P that charges the terminal  $V_m$  with parasitic capacitance and the next stage with input capacitance, a circuit group Q for discharging, and an A-D converter that amplifies the analog voltage  $V_m$  to a digital logic level. The voltage  $V_m$  is determined by the values of input signals A and B, regardless of the circuit of the next stage.

As shown in FIG. 1A, a spin transistor is contained in at least one of the circuit groups P and Q, and the current control capacity can be controlled in accordance with the magnetization state of the spin transistor. Therefore, even if the input signals A and B have the same values, the voltage  $V_m$  varies depending on the magnetization state of the spin transistor.

The variation of  $V_m$  caused by a change in the magnetization sate of the spin transistor is amplified to the digital logic level by the A-D converter having a predetermined logic threshold value, thereby forming a reconfigurable logic circuit. Alternatively, with an A-D converter that can change the logic 5 threshold value using the spin transistor, a reconfigurable logic circuit can be formed.

The circuit shown in FIG. 1B has a 2-input v-MOS structure with equally weighted inputs. In a symmetric function, the input signals A and B do not need to be distinguished from each other. Accordingly, with the 2-input v-MOS structure having equally weighted inputs, inputs can be efficiently performed to the circuit groups. If there is a need to distinguish the input signals A and B from each other, the weights on the input capacity should be made different from each other 15 between the input signals A and B.

The circuit in accordance with the present invention contains ferromagnetic bodies made of a ferromagnetic metal or the like. This circuit is a non-volatile, reconfigurable circuit, and more particularly, is a logic circuit that employs a spin transistor that can control its transfer characteristics in accordance with the spin direction of the conduction carriers or the magnetization states of the ferromagnetic bodies. Using the spin transistor, a symmetric Boolean function can be realized with a small number of components.

In the following, the spin transistor is described in greater detail. The spin transistor has at least one ferromagnetic body (free layer) with a magnetization direction that can be independently controlled with a magnetic field or the like, and at least one ferromagnetic body (pin layer) with a fixed magnetization direction. In this spin transistor, the relative magnetization state between the free layer and the pin layer can be switched between parallel magnetization and antiparallel magnetization by changing the magnetization direction of the free layer.

In the spin transistor, output characteristics in accordance with the magnetization state inside can be realized by virtue of the conduction phenomena, such as spin-dependent scattering, a spin-dependent tunneling effect, and a spin filter effect, which depend on the spin direction of the carriers and 40 the magnetization directions of the ferromagnetic bodies. Accordingly, the transfer characteristics of the spin transistor can be controlled in accordance with the relative magnetization direction of the pin layer with respect to the free layer contained in the spin transistor, even when the same biases are 45 applied.

In the following, an example case where the spin transistor is a MOSFET spin transistor (hereinafter referred to as "spin MOSFET") is described. Although spin-dependent conduction phenomena are included, the transistor operation is based 50 on the same principles as those of the operation of a conventional MOSFET. Particularly, the output characteristics can be represented by gradual channel approximation.

FIG. 2A illustrates an example structure of a spin MOS-FET. As shown in FIG. 2A, the spin MOSFET (A) is formed 55 on a semiconductor (substrate) 1, and has the same structure as a conventional MOSFET, including the aspect that a gate electrode 7 is formed on a gate insulating film 11. The spin MOSFET (A) differs from a conventional MOSFET in that a source electrode 3 and a drain electrode 5 are made of a ferromagnetic material. Hereinafter, the source electrode made of a ferromagnetic source 3, and the drain electrode made of a ferromagnetic material will be referred to simply as the ferromagnetic drain 5. In the drawings, "FM" indicates "ferromagnetic metal", but the source and drain may be made of some other electric conductive ferromagnetic material.

8

The ferromagnetic source 3 serves as a spin injector that injects spin-polarized carriers to a channel formed below the gate in the semiconductor 1. The ferromagnetic drain 5 serves as a spin analyzer that detects an electric signal representing the direction of the spins injected to the channel. In a case where a ferromagnetic metal (FM) is employed as the ferromagnetic material, the ferromagnetic source 3 and the ferromagnetic drain 5 are formed with the Schottky junctions with the semiconductor (substrate) 1. A gate voltage is applied to the gate electrode 7, so that spin-polarized carriers can be injected from the ferromagnetic source 3 to the channel via a Schottky barrier.

The injected spin-polarized carriers reach the ferromagnetic drain 5 via the channel (for ease of explanation, the Rashba effect caused by the gate field of the spin-polarized carriers injected to the channel is ignored). In a case where parallel magnetization is observed between the source and the drain, the spin-polarized carriers injected to the ferromagnetic drain 5 become a drain current, without adverse influence of spin-dependent scattering. In a case where antiparallel magnetization is observed, on the other hand, the ferromagnetic drain 5 is subjected to the resistance due to spin-dependent scattering. Accordingly, in the spin MOS-FET, the current drive force varies depending on the relative magnetization direction between the source and the drain.

FIGS. 3A and 3B show idealized static characteristics of a spin MOSFET. With a gate voltage equal to or lower than a threshold value  $(V_{gs} < V_{th})$ , the spin MOSFET is in an OFF state, as in the case of a conventional MOS transistor. This does not change with the magnetization state of the spin MOSFET. When a gate voltage equal to or higher than the threshold value ( $V_{gs}=V_{gs1}< V_{th}$ ) is applied, the spin MOSFET is put into an ON state. However, even when the same gate voltage is applied, the drain current  $I_d$  varies depending on the 35 magnetization state of the ferromagnetic bodies included in the spin MOSFET. In the case of parallel magnetization, a high drain current  $I_{d\uparrow\uparrow}$  flows. In the case of antiparallel magnetization, a low drain current  $I_{d\uparrow\downarrow}$  flows. If the drain current of the spin MOSFET can be represented using the same gain coefficient as that of a conventional MOSFET, the gain coefficient is high in the case of parallel magnetization, and the gain coefficient is low in the case of antiparallel magnetization. In the following, relative parameters  $\beta$  representing the gain coefficients of the spin MOSFETs and the MOSFETs are introduced. With the gain coefficients of the spin MOSFETs and the MOSFETs included in the circuit being  $\beta_{G1}$ ,  $\beta_{G2}$ ...  $\beta_{GN}$  (for the spin MOSFET, the gain coefficient in the case of parallel magnetization is set separately from the gain coefficient in the case of antiparallel magnetization), the gain coefficient of the spin MOSFETs and the MOSFETs can be expressed as  $\beta_{G1} = \beta_1 \beta_{G1}$ ,  $\beta_{G2} = \beta_2 \beta_{G1}$ ,  $\beta_{G3} = \beta_3 \beta_{G1}$ ...  $\beta_{GN} = \beta_N \beta_{G1}$ , using the gain coefficient  $\beta_{G1}$ . With the coefficients  $\beta_1(=1)$ ,  $\beta_2, \dots, \beta_N$ , the magnitude correlation among the gain coefficients of the transistors can be expressed. Although the magnitude correlation among the gain coefficients  $\beta_1$ ,  $\beta_2, \ldots, \beta_N$  is expressed with given numerals, the numeric values  $\beta$  are merely examples of representations of the magnitude correlation, and those numeric values do not limit the scope of the present invention. Also, the magnitude correlation among the gain coefficients  $\beta_1, \beta_2, \dots, \beta_N$  indicates an example of the magnitude correlation among output currents when the same bias is applied to the MOSFET and the spin MOSFET, including a case where the output characteristics of the spin MOSFET cannot be expressed with the output characteristics of the conventional MOSFET.

Next, a vMOS structure is described in conjunction with FIG. **2**B and FIG. **4**. As shown in FIG. **2**B, a MOSFET (B)

with a vMOS structure includes a source 13 and a drain 15 that are formed on a semiconductor 11, a floating gate 21 formed above the semiconductor 11 via a gate insulating film 20, and two divided gate electrodes 17a and 17b. As described above, inputs A and B are input to the gates 17a and 17b of the 5 vMOS structure via the input capacitances of the gate electrode and the floating gate. The inputs can be weighted by varying the magnitudes of the gate electrode and the floating gate. Here, a case where all the input capacitances are equal to one another is described as an example.

In the 2-input vMOS structure shown in FIG. 2B, the potential  $V_{fg}$  of the floating gate 21 is represented by the input mean value, which is  $V_{fg} = (A+B)/2$ , obtained by coupling of capacitances in a case where the gate capacitance can be ignored. Likewise, in a case of multiple inputs (n inputs 15 (n>2), it is safe to assume that the mean value of the n inputs is input to the floating gate. FIG. 4 shows the static characteristics in a case where the inputs A and B are digital values. However, the inputs may be analog values. As shown in FIG. **4.** in the case of A=B="0", the drain current  $I_d$  hardly flows. In 20 the case of A=B="1", the drain current I<sub>d</sub> flows. When either A or B is "1", the drain current that is equivalent to that obtained by applying a gate voltage half the above described gate voltage is generated. In the symmetric function, the input signals A and B do not need to be distinguished from each other. Accordingly, using the equally-weighted 2-input vMOS structure, input can be efficiently performed to the circuit groups.

An AND/OR reconfigurable logic circuit can be realized using the inputs of the vMOS structure and an inverter structure having an E/E configuration, an E/D configuration, or a CMOS configuration formed with spin MOSFETS and conventional MOSFETS as the circuit structure of the circuit group P and the circuit group Q. FIGS. 5A, 5B, and 5C illustrate AND/OR reconfigurable logic circuits using the 35 inverter structures of the E/E configuration, the E/D configuration, and the CMOS configuration. Hereinafter, each spin MOSFET will be indicated by a transistor symbol with an arrow. In the drawings, spin MOSFETs are used for active loads (Q2) of the inverters of the E/E configuration, the E/D 40 configuration, and the CMOS configuration. However, spin MOSFETs may be used for drivers (Q1). Alternatively, both the active loads (Q2) and the drivers (Q1) may be formed with spin MOSFETs. The input vMOS structure is used for the drivers (Q1) in the E/E configuration and the E/D configura- 45 tion. In the CMOS configuration, the vMOS structure is realized with a floating gate shared between Q2 and Q1. The inverter in the output stage is used to divide the output of  $V_m$ into the logic levels of "1" and "0". This inverter serves as an A-D converter. The active load Q2 in each of FIGS. 5A 50 through 5C forms the circuit group P, while the driver Q1 forms the circuit group Q. Further, an extra circuit for controlling the potential of  $V_m$  in each of the circuits of FIGS. 5A through 5C is added to the circuit group P and the circuit group Q, thereby achieving a complicated, reconfigurable 55 ingly, the output  $V_{out}$  is "1". logic circuit.

As shown in FIG. 6, it is also possible to achieve the operation equivalent to that of the vMOS structure by employing CMOS inverters for inputs, instead of the capacitance coupling. In such a case, however, a logic function that 60 is obtained by inverting the logic function of FIGS. 5A through 5C is output.

Next, a reconfigurable logic circuit in accordance with a first embodiment of the present invention is described in conjunction with the accompanying drawings. In the logic circuit in accordance with this embodiment, the driver or the active load of an E/D inverter circuit formed with an enhance10

ment MOSFET and a depletion MOSFET is replaced with a spin MOSFET. To replace the driver, an enhancement spin MOSFET should be employed. To replace the active load, a depletion spin MOSFET should be employed. The input vMOS structure is used for the driver. As for the inverter of the output stage, a CMOS inverter is most preferred in terms of performance, but it is possible to employ an inverter of another type, such as an E/D inverter.

The load curve in the E/E configuration varies according to the voltage generated in the driver. With the E/D configuration, on the other hand, the load curve with the active load is saturated. Accordingly, a wider logic margin can be allowed.

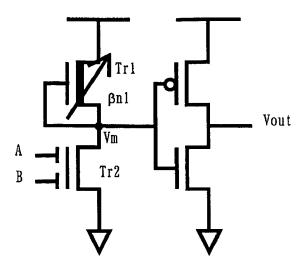

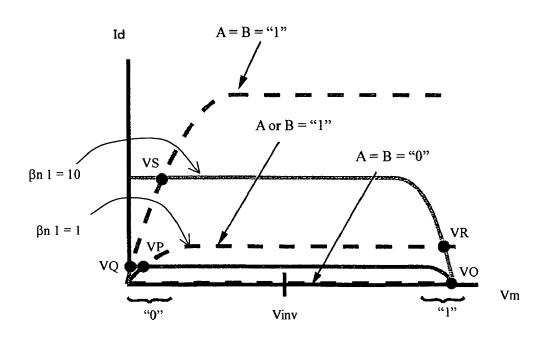

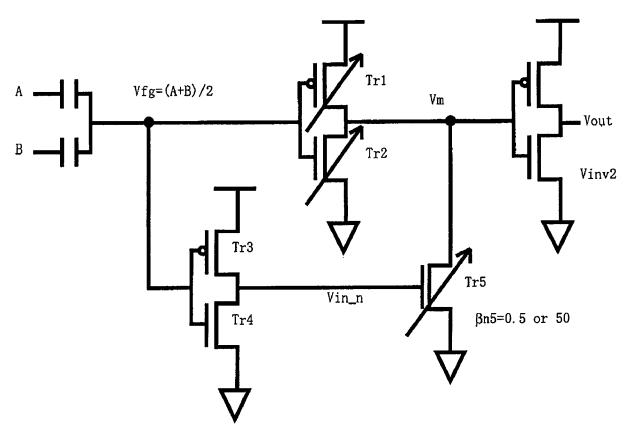

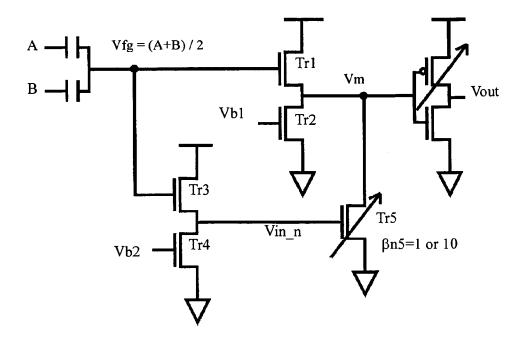

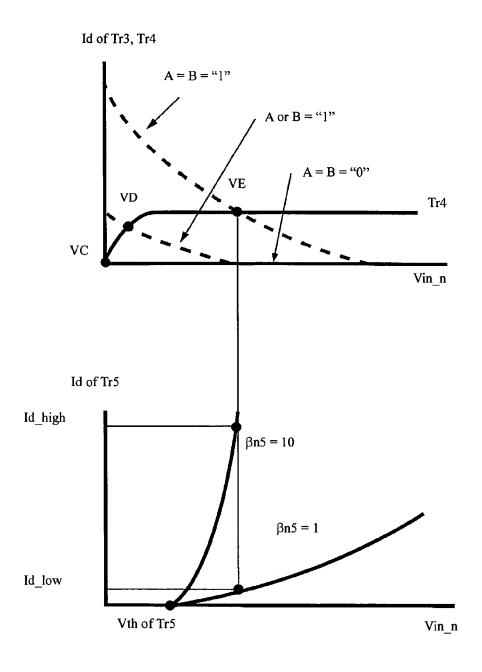

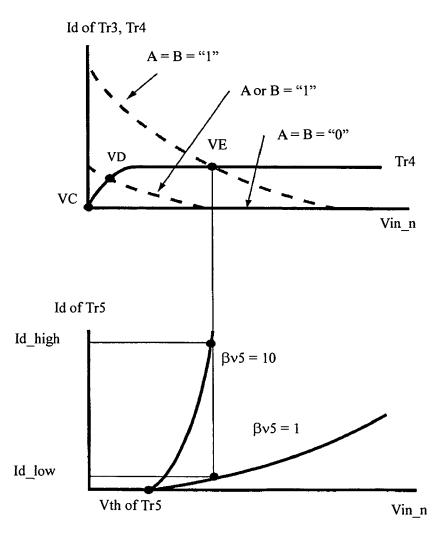

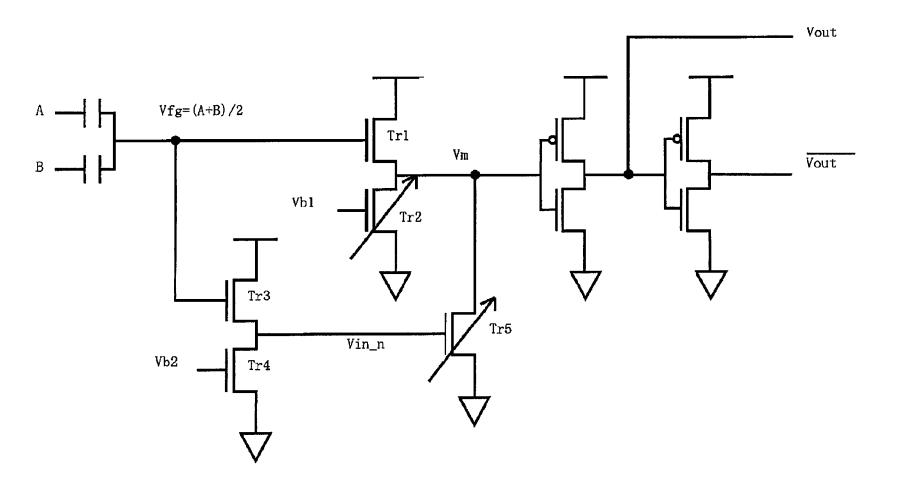

1) AND/OR Circuit

Referring now to FIGS. 7 through 9, an AND/OR circuit with a n-channel spin MOSFET of a depletion type is described. In FIG. 7, the n-channel spin MOSFET of a depletion type is denoted by Tr1, and the parameter  $\beta_{n1}$  can be 1 or 10 in the case of antiparallel magnetization or parallel magnetization. Since the source and the gate of Tr1 are shortcircuited, the load curve is saturated with respect to Vm as indicated by the solid line in FIG. 8. A vMOS structure is used for the input of a transistor Tr2, and its operation can be as indicated by the broken line in FIG. 8. FIGS. 9A and 9B are the truth tables of this circuit. Also, the details of the operation 25 are shown in Table 1.

TABLE 1

| • |              |        |                       | V <sub>m</sub>            |                                                                                          |            |                              |            |           |

|---|--------------|--------|-----------------------|---------------------------|------------------------------------------------------------------------------------------|------------|------------------------------|------------|-----------|

|   | $\beta_{n1}$ | A<br>B | 0                     | 0<br>1                    | 1<br>1                                                                                   | (in c      | V <sub>out</sub><br>order of | Vm)        | function  |

|   | 1<br>10      |        | $V_O("1") \ V_O("1")$ | $V_{P}("0") \ V_{R}("1")$ | $\begin{matrix} \mathbf{V}_{Q}(\text{``0"}) \\ \mathbf{V}_{S}(\text{``0"}) \end{matrix}$ | "0"<br>"0" | "1"<br>"0"                   | "1"<br>"1" | OR<br>AND |

In a case where the circuit functions as an OR circuit, the spin MOSFET is put into the antiparalell magnetization configuration, and the parameter  $\beta_{n1}$  is set at 1, with which the current driving capacity is small. Here, in the case of A=B="0", the operating point  $V_m$  is  $V_0$  according to FIG. 8, and the output  $V_{out}$  is inverted and amplified to "0". In the case of A or B="1" (hereinafter, (A, B)=("1", "0") or (A, B)=("0", "1") will be expressed simply as A or B="1"), the operating point  $V_m$  is  $V_P$ , and accordingly, the output  $V_{out}$  is "1". In the case of A=B="1", the operating point  $V_m$  is  $V_Q$ , and accordingly ingly, the output  $V_{out}$  is "1".

In a case where the circuit functions as an AND circuit, the spin MOSFET is put into the paralell magnetization configuration, and the parameter  $\beta_{n1}$  is set at 10, with which the current driving capacity is large. Here, in the case of A=B="0", the operating point  $V_m$  is  $V_0$ , and accordingly, the output  $V_{out}$  is "0". In the case of A or B="1", the operating point  $V_m$  is  $V_R$ , and accordingly, the output  $V_{out}$  is "0". In the case of A=B="1", the operating point  $V_m$  is  $V_S$ , and accord-

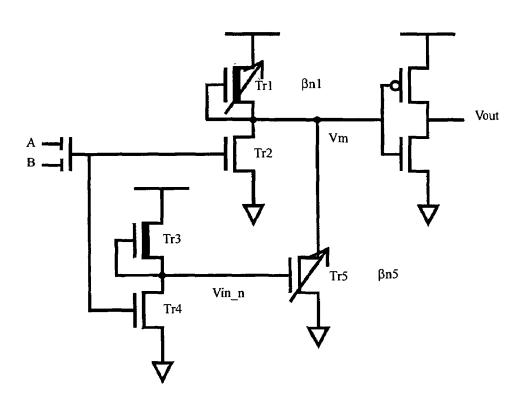

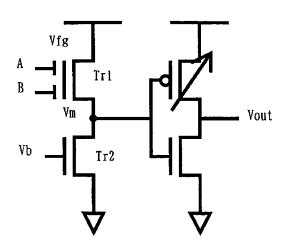

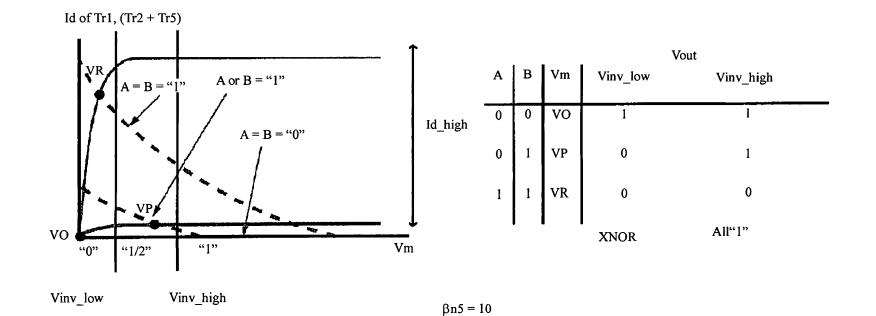

# 2) AND/OR/XNOR Circuit

FIG. 10 illustrates a circuit in which an XNOR function is added to the circuit shown in FIG. 7. The XNOR function is added as a Q group that is a circuit in which the input/output correlation is the same as that in an AND circuit, in the case of A or B="0" and A=B="1", and  $V_{out}$  is "1" ( $V_m$  is "0") in the case of A=B="0". In FIG. 10, the transistors Tr3 through Tr5 are the added part. The transistors Tr3 and Tr4 that forms an inverter serve as a level shifter. As shown in FIG. 11, the transistor Tr5 is energized (is put into an ON state) only when A and B are "0". The transistor Tr5 is a spin MOSFET, but the variation of  $\beta_{n5}$  according to the magnetization state is

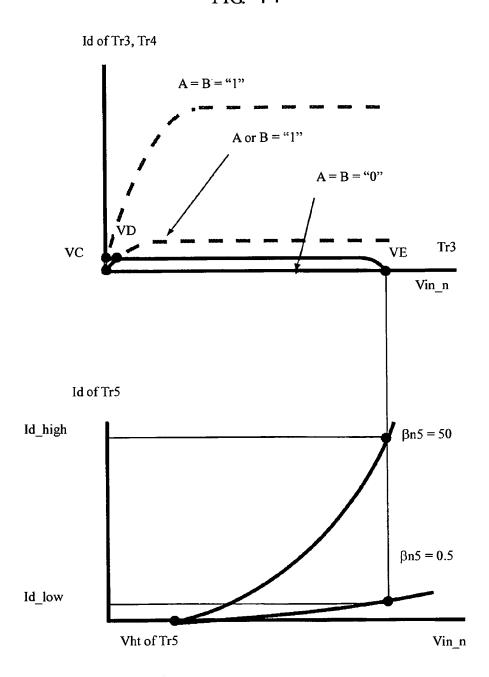

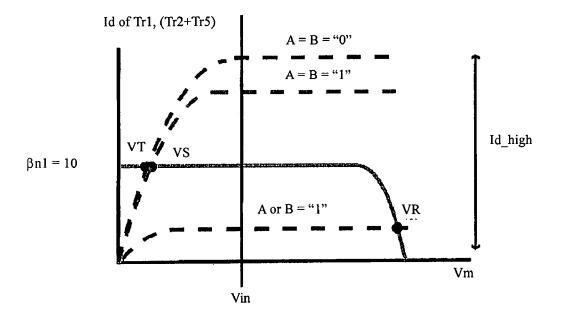

designed to be greater than the variation of  $\beta_{n1}$  of the transistor 1. For example,  $\beta_{n5}$  is 0.5 or 50 in the case of antiparallel magnetization or parallel magnetization. In the case of parallel magnetization,  $\beta_{n5}$  is 50, with which a sufficiently high current ( $I_{d\_high}$ ) flows. In the case of antiparallel magnetization,  $\beta_{n5}$  is 0.5, with which the current value ( $I_{d\_low}$ ) is very small. FIGS. 12A through 14B show the operating point  $V_m$  with respect to each parameter  $\beta$ . The sum of currents flowing through the transistors Tr2 and Tr5 is indicated by solid lines, and the current  $I_{d\_low}$  can be ignored. The circuit functional 10 correlation between  $\beta_{n1}$  and  $\beta_{n5}$  is shown in Table 2.

TABLE 2

|                                  |        |                       | V,,                                                                                                             |                                              |                          |                          |                          | _                            |

|----------------------------------|--------|-----------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------|--------------------------|--------------------------|------------------------------|

| $\beta_{n1}$ $\beta_{n5}$        | A<br>B | 0<br>0                | O<br>1                                                                                                          | (in c                                        | function                 |                          |                          |                              |

| 1 0.5<br>10 0.5<br>1 50<br>10 50 |        | $V_O("1") \ V_T("0")$ | $\begin{array}{c} V_P(\text{``0''}) \\ V_R(\text{``1''}) \\ V_R(\text{``1''}) \\ V_R(\text{``0''}) \end{array}$ | V <sub>S</sub> ("0")<br>V <sub>S</sub> ("0") | "0"<br>"0"<br>"1"<br>"1" | "1"<br>"0"<br>"0"<br>"1" | "1"<br>"1"<br>"1"<br>"1" | OR<br>AND<br>XNOR<br>all "1" |

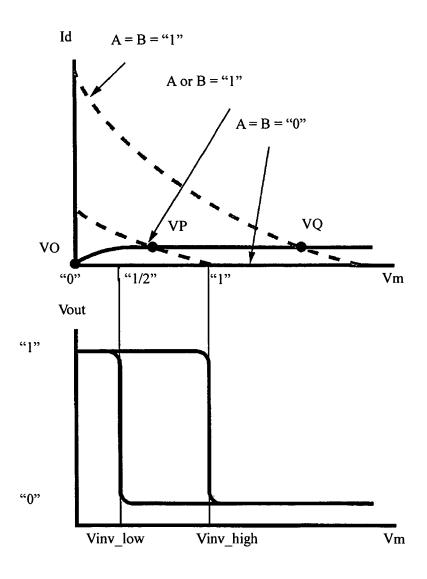

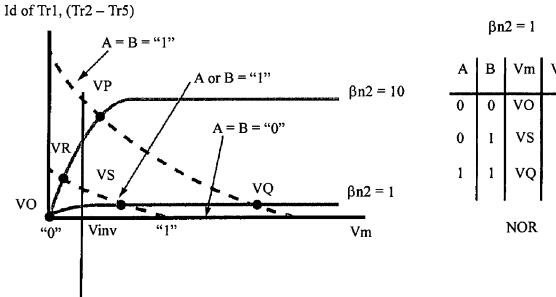

Referring first to FIGS. **12**A through **12**C, the AND/OR function is described. The transistor Tr**5** is put into an antiparalell magnetization configuration, and the current driving capacity is made very small ( $\beta_{ns}$ =0.5). By doing so, the flowing current I<sub>d\_low</sub> can be ignored, and the corresponding portion is regarded as open. As a result, the circuit has the same structure as that of the circuit shown in FIG. **7**, and the AND(FIG. **12**C)/OR(FIG. **12**B) function can be maintained.

Next, the XNOR function is described in conjunction with FIGS. 13A and 13B. The transistor Tr5 is put into a paralell magnetization configuration, and the current driving capacity is made high ( $\beta_{n5}$ =50). The transistor Tr2 is also put into a 35 paralell magnetization configuration ( $\beta_{n1}$ =10) as in the case of AND. In the case of A=B="1" or A or B="1", the transistor Tr5 is regarded as open, and accordingly, functions as an AND circuit. In the case of A=B="0",  $V_m$  is discharged by the current  $I_{d\_high}$  of the transistor Tr5, to obtain  $V_m = V_T < V_{inv}$  and 40  $V_{out}$ ="1". Further, when the transistor Tr1 is put into an antiparalell magnetization configuration ( $\beta_{n1}=1$ ) and the transistor Tr5 is put into a paralell magnetization configuration ( $\beta_{n5}$ =50),  $V_{out}$  becomes "1" for all the inputs (see FIGS. 14A and 14B). This circuit is characterized in that the oper- 45 ating point  $V_m$  is always close to 0V or  $V_{dd}$ , and the logic margin is wide.

# 3) AND/OR/XNOR/NAND/NOR/XOR Functions

In a circuit shown in FIG. 15, another stage of an inverter circuit is added to the output. The details of the operation of this circuit are shown in Table 3. Basically, this circuit is the same as the circuit illustrated in FIG. 10, but all the symmetric Boolean functions can be realized with  $V_{out}$  and its inverted output.

TABLE 3

|              | _            |                | V,  | aut    |        |        | $\overline{V}_{c}$ |        |     |                     |

|--------------|--------------|----------------|-----|--------|--------|--------|--------------------|--------|-----|---------------------|

| $\beta_{n1}$ | $\beta_{n5}$ | A 0 0<br>B 0 1 |     | 0<br>1 | 1<br>1 | A<br>B | 0                  | 0<br>1 | 1   | function            |

| 1            | 0.5          |                | "0" | "1"    | "1"    |        | "1"                | "0"    | "0" | OR/NOR              |

| 10           | 0.5          |                | "0" | "0"    | "1"    |        | "1"                | "1"    | "0" | AND/NAND            |

| 1            | 50           |                | "1" | "0"    | "1"    |        | "0"                | "1"    | "0" | XNOR/XOR            |

| 10           | 50           |                | "1" | "1"    | "1"    |        | "0"                | "0"    | "0" | all "1"/<br>all "0" |

12

Next, a reconfigurable logic circuit in accordance with a second embodiment of the present invention is described in conjunction with the accompanying drawings. A logic circuit in accordance with this embodiment can be formed by using a spin MOSFET for either the n-channel MOSFET or the p-channel MOSFET in a CMOS inverter, or using spin MOSFETs for both the n-channel MOSFET and the p-channel MOSFET. The vMOS structure used for the input is formed with a floating gate shared by the n-channel device and the p-channel device. The inverter of the output stage is a conventional inverter of the CMOS configuration.

In accordance with this embodiment, the operating curve is saturated as in the E/D configuration, and accordingly, the mean logic margin can be made wider. Also, it is effective for low power consumption.

## 1) Threshold Value Variable Inverter

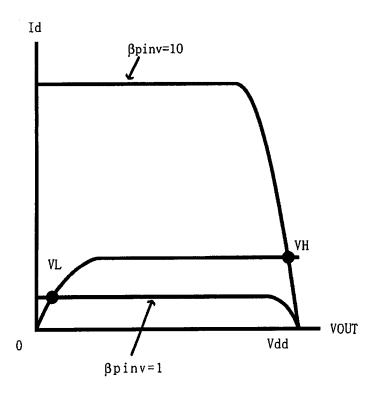

FIG. 16A is a circuit diagram of an inverter having a variable logic threshold value. In this circuit, the n-channel MOS-FET and the p-channel MOSFET of a conventional CMOS inverter are replaced with a p-channel spin MOSFET. Here, the current driving capacity of the p-channel spin MOSFET in the case of parallel magnetization and antiparallel magnetization is made p<sub>inv</sub>=1 or 10, and the current driving capacity of the n-channel spin MOSFET is a value between 1 and 10. The logic threshold value of the inverter circuit shown in FIG. **16**A varies according to the combination of parameters  $\beta$ . FIG. 16B shows the characteristics of both spin MOSFETs in a case where the parameter  $\beta_{ninv}$  is fixed while the parameter  $\beta_{pinv}$  is set to 1 or 10. Although the input is constant, the output  $V_{out}$  is  $V_L$  of the low level when the parameter  $\beta_{pinv}$  is 1, and the output  $V_{out}$  is  $V_H$  of the high level when the parameter  $\beta_{pinv}$  is 10. In this manner, the output  $V_{out}$  varies according to the current driving capacity of the p-channel spin MOSFET. More quantitatively, this can be explained as follows.

The inverter circuit shown in FIG. 16A can be considered as the same as a conventional CMOS inverter. In such a case, the p-channel spin MOSFET and the n-channel spin MOSFET operate in the saturation region. With the drain current  $\mathbf{I}_d$  flowing through the n-channel spin MOSFET and the p-channel spin MOSFET, the following equation can be obtained:

$$V_{inv} = \frac{V_{dd} - |V_{thp}| + V_{thn} \sqrt{\beta_{inv}}}{1 + \sqrt{\beta_{inv}}}$$

where

$$\beta_{inv} = \frac{\beta_{ninv}}{\beta_{pinv}}$$

Here, the logic threshold value  $V_{im}$  is plotted as the function of the driving force ratio  $\beta_{im}=\beta_{nim}/\beta_{pim}$  in FIG. 17, with  $V_{dd}$  being 3.3V and  $V_{thm}$  being  $|V_{thp}|$ =0.5V. As shown in FIG. 17, the threshold value according to the ratio  $\beta_{im}$ =0.1, 1, 10 can be obtained.

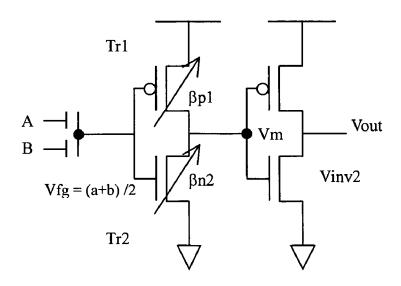

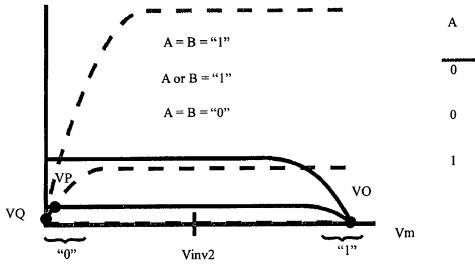

# 2) AND/OR

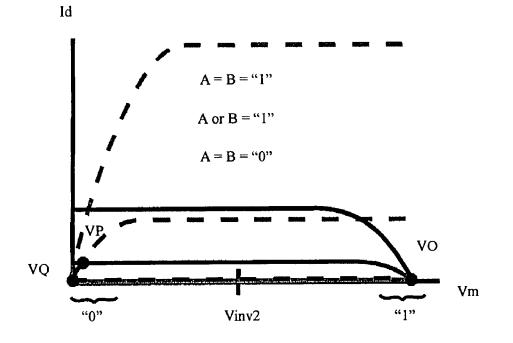

FIG. 18 illustrates an AND/OR circuit that employs the threshold value variable inverter shown in FIG. 16A. As shown in FIG. 18, the AND/OR circuit is formed with inverters of two stages. The inverter at the input side is a threshold value variable inverter, and the inverter at the output side is a conventional inverter (with a threshold value V<sub>inv2</sub>=V<sub>dd</sub>2). The operating characteristics of the circuit shown in FIG. 18 are shown in FIGS. 19A and 19B. In FIG. 19A, the solid line indicates the characteristics of the transistor Tr1, and the

broken line indicates the characteristics of the transistor Tr2. The details of the operation of this circuit are shown in Table 4.

TABLE 4

|              |              |        |                                                                                        | $V_m$                     |        |            |                              |             |           |

|--------------|--------------|--------|----------------------------------------------------------------------------------------|---------------------------|--------|------------|------------------------------|-------------|-----------|

| $\beta_{n1}$ | $\beta_{n2}$ | A<br>B | 0                                                                                      | 0<br>1                    | 1<br>1 | (in c      | V <sub>out</sub><br>order of | Vm)         | function  |

| 1<br>10      | 10<br>1      |        | $\begin{matrix} \mathbf{V}_O(\text{``1''}) \\ \mathbf{V}_O(\text{``1''}) \end{matrix}$ | $V_{P}("0") \ V_{R}("1")$ |        | "0"<br>"0" | "1"<br>"0"                   | "1 "<br>"1" | OR<br>AND |

## 2-1) OR

Referring now to FIGS. **19**A and **19**B, an OR circuit is described. In a case where the circuit illustrated in FIG. **18** functions as an OR circuit, the transistor Tr**1** is put into an antiparalell magnetization configuration ( $\beta_{p1}$ =1), and the transistor Tr**2** is put into a paralell magnetization configuration ( $\beta_{n2}$ =10). Here, in the case of A=B="0", the operating point V<sub>m</sub> is V<sub>0</sub> according to FIG. **19**A, and the output V<sub>out</sub> is inverted and amplified to "0". In the case of A or B="1", the operating point V<sub>m</sub> is V<sub>p</sub>, and the output V<sub>out</sub> is "1". In the case of A=B="1", the operating point V<sub>m</sub> is V<sub>Q</sub>, and the output V<sub>out</sub> is "1".

#### 2-2) AND

Referring now to FIGS. **20**A and **20**B, an AND circuit is described. The transistor Tr**1** is put into a paralell magnetization configuration ( $\beta_{p1}$ =10), and the transistor Tr**2** is put into 30 an antiparalell magnetization configuration ( $\beta_{n2}$ =1). Here, in the case of A=B="0", the operating point  $V_m$  is  $V_0$ , and the output  $V_{out}$  is inverted and amplified to "0". In the case of A or B="1", the operating point  $V_m$  is  $V_Q$ , and the output  $V_{out}$  is "0". In the case of A=B="1", the operating point  $V_m$  is  $V_Q$ , and 35 the output  $V_{out}$  is "1".

As can be seen from FIGS. **21** through **23**B, the threshold value  $V_{inv1}$  of the threshold value variable inverter (formed with the transistors Tr**1** and Tr**2**) at the input side may be regarded as the reference value. In the following, the operation in such a case is described.

#### 2-3) OR

When the transistor Tr1 is put into an antiparalell magnetization configuration ( $\beta_{p1}=1$ ) and the transistor Tr2 is put into a paralell magnetization configuration ( $\beta_{n2}=10$ ) in a circuit illustrated in FIG. 21, the logic threshold value  $V_{inv1}$  becomes  $V_{inv1\_low} < V_{dd}/2$ , as shown in FIG. 22A. Also as shown in FIGS. 22A and 22B, in the case of A=B="0",  $V_{fg}$  becomes "0". Accordingly, the operating point  $V_m$  is  $V_0$ ="1", and the output  $V_{out}$  is "0". In the case of A or B="1",  $V_{fg}$  is  $V_{dd}/2 > V_{inv1\_low}$ . Accordingly, the operating point  $V_m$  is  $V_p$ ="0", and the output  $V_{out}$  is "1". In the case of A=B="1",  $V_{fg}$  is  $V_{dd}$ . Accordingly, the operating point  $V_m$  is  $V_p$ ="0", and the output  $V_{out}$  is "1".

#### 2-4) AND

When the transistor Tr1 is put into a paralell magnetization configuration ( $\beta_{p1}$ =10) and the transistor Tr2 is put into an antiparalell magnetization configuration ( $\beta_{n2}$ =1) in the circuit illustrated in FIG. 21, the logic threshold value  $V_{inv1}$  60 becomes  $V_{inv1\_high} > V_{dd}/2$ , as shown in FIG. 23A. In the case of A=B="0",  $V_{fg}$  becomes "0". Accordingly, the operating point  $V_m$  is  $V_0$ ="1", and the output  $V_{out}$  is "0". In the case of A or B="1",  $V_{fg}$  is  $V_{dd}/2 < V_{inv1\_low}$ . Accordingly, the operating point  $V_m$  is  $V_R$ ="1", and the output  $V_{out}$  is "0". In the case of A=B="1",  $V_{fg}$  is  $V_{dd}$ . Accordingly, the operating point  $V_m$  is  $V_0$ ="0", and the output  $V_{out}$  is "1".

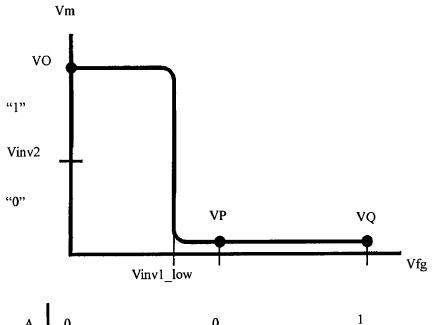

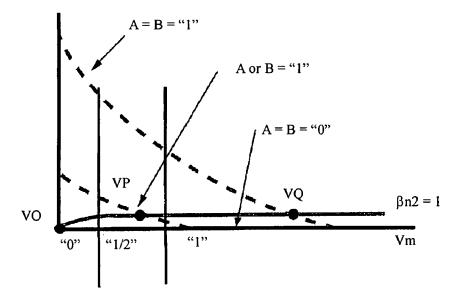

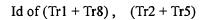

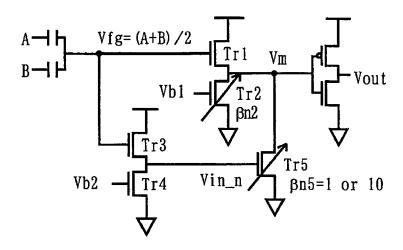

#### 3) AND/OR/XNOR

FIG. 24 illustrates an AND/OR/XNOR circuit. The principles of the operation are the same as in the case of the circuit shown in FIG. 10. In the XNOR circuit, the input/output correlation is the same as that in the AND circuit in the case where A=B="1" or A or B="1", but is different from that in the AND circuit only in the case where A=B="0", with  $\mathbf{V}_{out}$ being "1" ( $V_m$ ="0"). This function can be realized by adding a circuit formed with the transistors Tr3, Tr4, and Tr5 (an • 10 n-channel spin MOSFET) to the circuit group Q. The inverter (a level shifter) formed with the transistors Tr3 and Tr4 has a threshold value  ${\rm V}_{\it inv3}$  lower than  ${\rm V}_{\it dd}/2.$  Accordingly, only in the case where A=B="0",  $V_{im\_n}$  becomes "1", and the transistor Tr5 is turned on. The variation in the current driving capacity  $\beta_{n5}$  of the transistor Tr5 between parallel magnetization and antiparallel magnetization is wider than that in the case of the transistors Tr1 and Tr2, and  $\beta_{n5}$  is 0.5 (antiparallel magnetization) or 50 (parallel magnetization). In the case of parallel magnetization ( $\beta_{n5}$ =50), a sufficiently high current  $(I_{d\_high})$  flows, but in the case of antiparallel magnetization  $(\beta_{n5}=0.5)$ , the value of the current  $(I_{d\_low})$  is very small (see the upper and lower graphs in FIG. 25).

The details of the operation are shown in Table 5.

TABLE 5

|               |              |              |        |                      | $V_m$      |              |                                     |                |

|---------------|--------------|--------------|--------|----------------------|------------|--------------|-------------------------------------|----------------|

| $\beta_{p1}$  | $\beta_{n2}$ | $\beta_{n5}$ | A<br>B | 0<br>0               | 0 1<br>1 1 |              | $V_{out}$ (in order of Vm)          | function       |

| 1             | 10           | 0.5<br>0.5   |        |                      |            |              | "0" "1" "1"                         | OR<br>AND      |

| 10<br>1<br>10 | 10           | 50<br>50     |        | V <sub>T</sub> ("0") | $V_P("0")$ | $V_{O}("0")$ | "0" "0" "1" "1" "1" "1" "1" "0" "1" | all"1"<br>XNOR |

## 3-1) AND/OR (See FIGS. **26**A and **26**B, **27**A and **27**B)

As the transistor  $\text{Tr}\mathbf{5}$  is put into an antiparalell magnetization configuration ( $\beta_{n5}$ =0.5), the current  $I_{d\_low}$  can be ignored, and the transistor  $\text{Tr}\mathbf{5}$  can be regarded as open. Accordingly, the circuit becomes equivalent to the AND/OR circuit shown in FIG. 18.

# 3-2) XNOR (See FIGS. 29A and 29B)

The transistor Tr5 is put into a paralell magnetization configuration ( $\beta_{n5}$ =50). In the inverter part, the transistor Tr1 is put into a paralell magnetization configuration ( $\beta_{p1}=10$ ), and the transistor Tr2 is put into an antiparalell magnetization configuration ( $\beta_{n2}=1$ ), as in the AND circuit. In the case where A=B="1" or A or B="1", the transistor Tr5 is equivalent to an open circuit, and operates in the same manner as the AND circuit. In the case where A=B="0",  $V_m$  is discharged by the current  $I_{d\_high}$  of the transistor Tr5, so as to be  $V_m = V_S < V_{inv2}$ . Accordingly,  $V_{out}$  becomes "1". Where the transistor Tr1 is put into an antiparalell magnetization configuration ( $\beta_{p1}=1$ ), the transistor Tr2 is put into a paralell magnetization configuration ( $\beta_{n2}=10$ ), and the transistor Tr5 is put into a paralell magnetization configuration ( $\beta_{rs}$ =50), the output  $V_{out}$  becomes "1" for all the input patterns (see FIGS. 28A and 28B).

Although all symmetric Boolean functions can be realized by adding an inverter to the output of the circuit shown in FIG. **24**, a technique of achieving all the symmetric Boolean functions by adding a new circuit to the circuit group P is described below.

## 4) AND/OR/XNOR/XOR

FIG. 30 illustrates an AND/OR/XNOR/XOR circuit. In the XOR circuit, the input/output correlation is the same as that in the OR circuit in the case where A=B="1" or A or B="1", but

is different from that in the OR circuit only in the case where A=B="1", with  $V_{out}$  being "0". Accordingly, this function can be realized by adding a circuit with which  $V_{out}$  becomes "0" in the case where A=B="1". The XOR function can be achieved by employing the transistors Tr6, Tr7, and Tr8 (a 5 p-channel spin MOSFET) in a complementary manner together with the transistors Tr3, Tr4, and Tr5 (an n-channel spin MOSFET). The inverter formed with the transistors Tr6 and Tr7 has a threshold value  $V_{imv4}$  higher than  $V_{dd}/2$ . Accordingly, only in the case where A=B="1",  $V_{im\_n}$  becomes "0", 10 and the transistor Tr8 is turned on (see FIG. 31).

The variation in the current driving capacity  $\beta_{P8}$  of the transistor Tr8 between parallel magnetization and antiparallel magnetization is wider than that in the case of the transistors Tr1 and Tr2, and  $\beta_{P8}$  is 0.5 (antiparallel magnetization) or 50 (parallel magnetization). In the case of parallel magnetization ( $\beta_{8p}$ =50), a sufficiently high current ( $I_{d\_high}$ ) flows, but in the case of antiparallel magnetization ( $\beta_{p8}$ =0.5), the value of the current ( $I_{d\_Jow}$ ) is very small. FIGS. 32A and 32B and FIGS. 33A and 33B show the operating point  $V_m$  in the case of the transistor Tr8 is in the parallel magnetization configuration ( $\beta_{p8}$ =50) and the transistor Tr5 is in the antiparallel magnetization configuration ( $\beta_{p5}$ =0.5). The sum of currents flowing through the transistors Tr1 and Tr8 is indicated by solid lines, and the sum of currents flowing through the transistors Tr2 and Tr5 is indicated by broken lines. Here, the current  $I_{d\_low}$  is ignored.

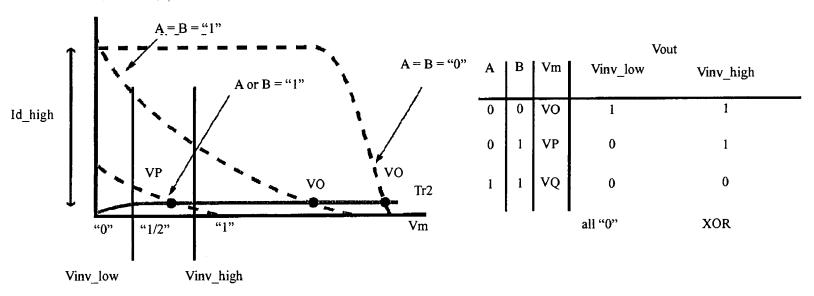

The operation of this circuit is shown in Table 6.

# 4-2) XOR (See FIGS. 32A and 32B)

The transistor Tr8 is put into a paralell magnetization configuration ( $\beta_{p8}$ =50). In the other parts, the transistor Tr1 is put into an antiparalell magnetization configuration ( $\beta_{p1}=1$ ), the transistor Tr2 is put into a paralell magnetization configuration ( $\beta_{n2}$ =10), and the transistor Tr**5** is put into an antiparalell magnetization configuration ( $\beta_{n5}$ =0.5), as in the OR circuit. In the case where A=B="0" or A or B="1", the transistor Tr8 is open, and operates in the same manner as the OR circuit. In the case where A=B="1",  $V_m$  is charged with the current  $I_{d\_high}$  of the transistor Tr8, so as to be  $V_m = V_T < V_{inv\_2}$ . Accordingly, V<sub>out</sub> becomes "0". Where the transistor Tr1 is put into a paralell magnetization configuration ( $\beta_{p1}=10$ ), the transistor Tr2 is put into an antiparalell magnetization configuration ( $\beta_{n2}=1$ ), the transistor Tr5 is put into an antiparalell magnetization configuration ( $\beta_{n5}$ =0.5), and the transistor Tr**8** is put into a paralell magnetization configuration ( $\beta_{p8}$ =50), the output V<sub>out</sub> becomes "0" for all the input patterns (see <sub>20</sub> FIGS. **33**A and **33**B).

# 5) AND/OR/XNOR/XOR/NAND/NOR

As in the case shown in FIG. 15, an inverter may be added to the output of the circuit shown in FIG. 24. However, it is possible to achieve the circuit by employing the circuit shown in FIG. 30. The transistor Tr5 in FIG. 30 functions only in the

TABLE 6

|       |              |              |              |        |                      | V,,,                   |              |       |                              |     |          |

|-------|--------------|--------------|--------------|--------|----------------------|------------------------|--------------|-------|------------------------------|-----|----------|

| β,,,1 | $\beta_{n2}$ | $\beta_{n5}$ | $\beta_{p8}$ | A<br>B | 0                    | 0<br>1                 | 1<br>1       | (in c | V <sub>out</sub><br>order of | Vm) | function |

| 1     | 10           | 0.5          | 0.5          |        | "1"                  | "0"                    | "0"          | "0"   | "1"                          | "1" | OR       |

| 10    | 1            | 0.5          | 0.5          |        | "1"                  | "1"                    | "0"          | "0"   | "0"                          | "1" | AND      |

| 1     | 10           | 50           | 0.5          |        | "0"                  | "0"                    | "0"          | "1"   | "1"                          | "1" | all "1"  |

| 10    | 1            | 50           | 0.5          |        | "0"                  | "1"                    | "0"          | "1"   | "0"                          | "1" | XNOR     |

| 1     | 10           | 0.5          | 50           |        | V <sub>O</sub> ("1") | $V_P("0")$             | $V_T("1")$   | "0"   | "1"                          | "0" | XOR      |

| 10    | 1            | 0.5          | 50           |        | $V_O("1")$           | $\mathbf{V}_{R}(``1")$ | $V_{T}("1")$ | "0"   | "0"                          | "0" | all "0"  |

# 4-1) AND/OR/XNOR

When the transistor Tr8 is put into an antiparalell magnetization configuration ( $\beta_{p8}$ =0.5) in the circuit shown in FIG. 30, the current flowing through the transistor Tr8 can be ignored, and the transistor Tr8 can be regarded as open. Accordingly, this circuit can be made equivalent to the circuit shown in FIG. 24, and the AND/OR/XNOR functions can be achieved by changing the magnetization states of the transistors Tr1, Tr2, and Tr5 (or the current driving capacities  $\beta_{p1}$ ,  $\beta_{n2}$ , and  $\beta_{n5}$ ).

case where A=B="0", and the operating point  $V_m$  is "0". The transistor Tr8 functions only in the case where A=B="1", and the operating point  $V_m$  is "1". Taking this fact into consideration, a NAND/NOR can be realized with the circuit shown in FIG. 30.

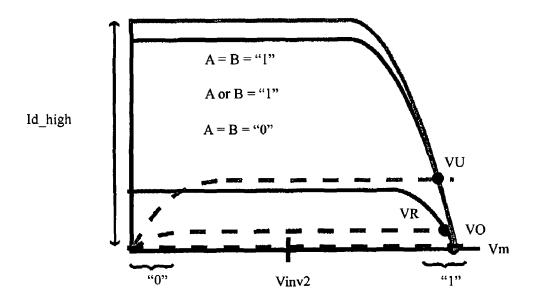

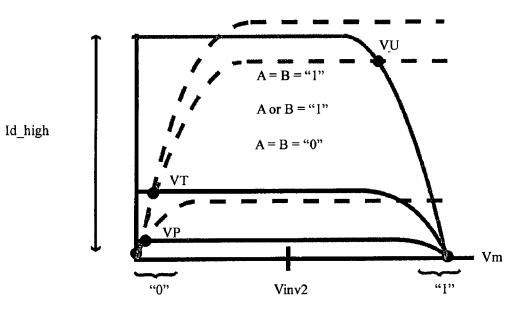

FIGS. **33**A and **33**B and FIGS. **34**A and **34**B show the operating points in the case where the transistors  $\text{Tr}\mathbf{5}$  and  $\text{Tr}\mathbf{8}$  are in a paralell magnetization configuration ( $\beta_{n5} = \beta_{p8} = 50$ ) in the circuit shown in FIG. **30**. The operations of the circuits are shown in Table 7.

TABLE 7

|          |              |              |              |   |                      | $V_m$                |                           |       |         |             |          |

|----------|--------------|--------------|--------------|---|----------------------|----------------------|---------------------------|-------|---------|-------------|----------|

| 0        | 0            | 0            | o            | A | 0                    | 0                    | 1                         | C     | Vout    | <b>V</b> /) | Ct'      |

| $p_{n1}$ | $\beta_{n2}$ | $\beta_{n5}$ | $\beta_{p8}$ | В | 0                    | 1                    | 1                         | (in c | rder of | VIII)       | function |

| 1        | 10           | 0.5          | 0.5          |   | "1"                  | "0"                  | "0"                       | "0"   | "1"     | "1"         | OR       |

| 10       | 1            | 0.5          | 0.5          |   | "1"                  | "1"                  | "0"                       | "0"   | "0"     | "1"         | AND      |

| 1        | 10           | 50           | 0.5          |   | "0"                  | "0"                  | "0"                       | "1"   | "1"     | "1"         | all"1"   |

| 10       | 1            | 50           | 0.5          |   | "0"                  | "1"                  | "0"                       | "1"   | "0"     | "1"         | XNOR     |

| 1        | 10           | 0.5          | 50           |   | "1"                  | "0"                  | "1"                       | "0"   | "1"     | "0"         | XOR      |

| 10       | 1            | 0.5          | 50           |   | "1"                  | "1"                  | "1"                       | "0"   | "0"     | "0"         | all "0"  |

| 1        | 10           | 50           | 50           |   | V <sub>7</sub> ("0") | $V_{p}("0")$         | V <sub>L</sub> ("1")      | "1"   | "1"     | "0"         | NAND     |

| 10       | 1            | 50           | 50           |   | V <sub>S</sub> ("0") | V <sub>R</sub> ("1") | V <sub>\(\nu("1")\)</sub> | "1"   | "0"     | "0"         | NOR      |

#### 5-1) AND/OR

When the transistor Tr**5** is put into an antiparalell magnetization configuration ( $\beta_{n5}$ =0.5) and the transistor Tr**8** is put into an antiparalell magnetization configuration ( $\beta_{p8}$ =0.5), the transistors Tr**5** and Tr**8** are both open. Accordingly, this 5 circuit is equivalent to the circuit shown in FIG. **28**.

# 5-2) XNOR

When the transistor Tr5 is put into a paralell magnetization configuration ( $\beta_{n5}$ =50) and the transistor Tr8 is put into an antiparalell magnetization configuration ( $\beta_{p8}$ =0.5), the transistor Tr8 is open. Accordingly, this circuit is equivalent to the circuit shown in FIG. 24.

#### 5-3) XOR

When the transistor Tr**5** is put into an antiparalell magnetization configuration ( $\beta_{n5}$ =0.5) and the transistor Tr**8** is put 15 into a paralell magnetization configuration ( $\beta_{p8}$ =50), the circuit becomes an XOR equivalent to the circuit shown in FIGS. **32**A and **32**B.

# 5-4) NAND (See FIGS. 34A and 34B)

The transistor Tr1 is put into an antiparalell magnetization 20 configuration ( $\beta_{p1}=1$ ), the transistor Tr2 is put into a paralell magnetization configuration ( $\beta_{n2}=10$ ), the transistor Tr5 is put into a paralell magnetization configuration ( $\beta_{n5}=50$ ), and the transistor Tr8 is put into a paralell magnetization configuration ( $\beta_{p8}=50$ ). In the case where A=B="0", discharging is 25 performed by the transistor Tr5, and the operating point  $V_m$  becomes  $V_T < V_{inv2}$ . Accordingly, the output  $V_{out}$  becomes "1". In the case where A or B is "1", the operating point  $V_m$  becomes  $V_P < V_{inv2}$ , and accordingly, the output  $V_{out}$  becomes "1". In the case where A=B="1",  $V_m$  is charged by the transistor Tr8, so as to be  $V_m = V_U > V_{inv2}$ . Accordingly,  $V_{out}$  becomes "0".

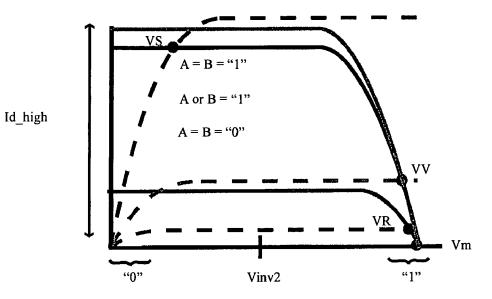

# 5-5) NOR (See FIGS. 35A and 35B)

The transistor Tr1 is put into a paralell magnetization configuration ( $\beta_{p1}$ =10), the transistor Tr2 is put into an antiparalell magnetization configuration ( $\beta_{n2}$ =1), the transistor Tr5 is put into a paralell magnetization configuration ( $\beta_{ns}$ =50), and the transistor Tr8 is put into a paralell magnetization configuration ( $\beta_{ps}$ =50). In the case where A=B="0", charging is performed by the transistor Tr5, and the operating point V<sub>m</sub> becomes V<sub>S</sub><V<sub>inv2</sub>. Accordingly, the output V<sub>out</sub> becomes "1". In the case where A or B is "1", the operating point V<sub>m</sub> becomes V<sub>R</sub>>V<sub>inv2</sub>, and accordingly, the output V<sub>out</sub> becomes "0". In the case where A=B="1", V<sub>m</sub> is charged by the transistor Tr8, so as to be V<sub>m</sub>=V<sub>p</sub>>V<sub>inv2</sub>. Accordingly, 45 V<sub>out</sub> becomes "0".

In the circuit shown in FIG. 30, the number of MOSFETs is 10, and the number of capacitors is 2. As this circuit can be realized with a CMOS configuration, the circuit layout can be made very compact.

FIG. 36 shows a circuit in which CMOS inverters using spin MOSFETs are connected in two stages. Each of the first-stage inverter and the second-stage inverter has an input of a vMOS structure. In this circuit, the same weighting is set on inputs A and B. The inputs A and B are input to the 55 second-stage inverter, and the output  $V_{m1}$  of the first stage is also input to the second-stage inverter. The capacitance weighting is the same between the inputs A and B in the second-stage inverter, but the capacitance weighting differs between the input A (or B) and the output  $V_{m1}$ . For example, 60 with the input capacitance with  $V_{m1}$  being  $C_{m1}$ , the relationship of  $3C_{m1}=C_A$  (= $C_B$ ) should be established. In this logic circuit, the magnetization states of Q1, Q2, and Q4 are changed to rewrite the logic functions. With the output  $V_{m1}$ , the logic functions of NOR and NAND can be realized. With the output  $V_{m2}$ , the logic functions of XNOR, XOR, AND, OR, all "1", and all "0" can be realized. Since the logic

18

amplitude may not reach the "0" level or "1" level with the outputs  $V_{m1}$  and  $V_{m2}$ , depending on the logic function, it is preferable that a CMOS inverter or the like is added to each output to amplify the signal. In such a case, however, the logic function is inverted. Also, it is possible to employ a spin MOSFET for Q2.